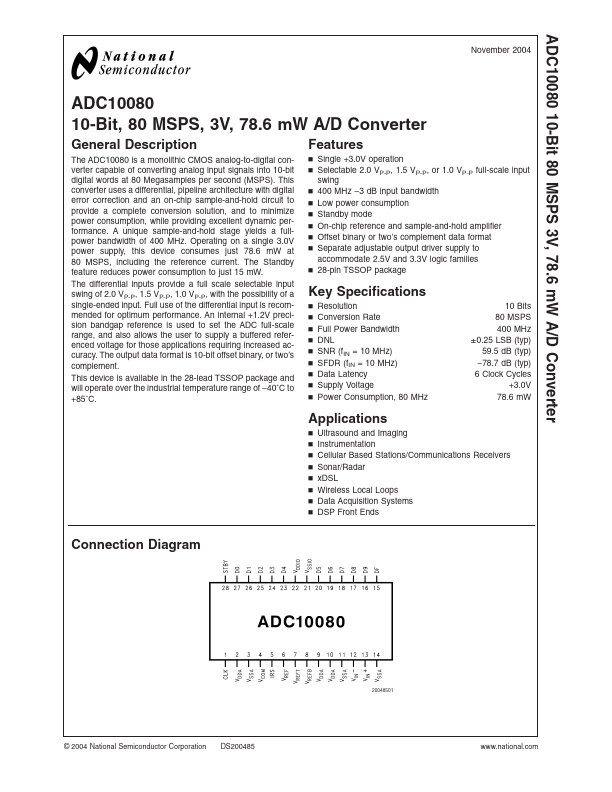

ADC10080

Overview

The ADC10080 is a monolithic CMOS analog-to-digital converter capable of converting analog input signals into 10-bit digital words at 80 Megasamples per second (MSPS). This converter uses a differential, pipeline architecture with digital error correction and an on-chip sample-and-hold circuit to provide a complete conversion solution, and to minimize power consumption, while providing excellent dynamic performance.

- Single +3.0V operation

- Selectable 2.0 VP-P, 1.5 VP-P, or 1.0 VP-P full-scale input swing

- 400 MHz -3 dB input bandwidth

- Low power consumption

- Standby mode

- On-chip reference and sample-and-hold amplifier

- Offset binary or two’s complement data format

- Separate adjustable output driver supply to accommodate 2.5V and 3.3V logic families

- 28-pin TSSOP package Key Specifications n n n n n n n n

- Resolution Conversion Rate Full Power Bandwidth DNL SNR (fIN = 10 MHz) SFDR (fIN = 10 MHz) Data Latency Supply Voltage Power Consumptio