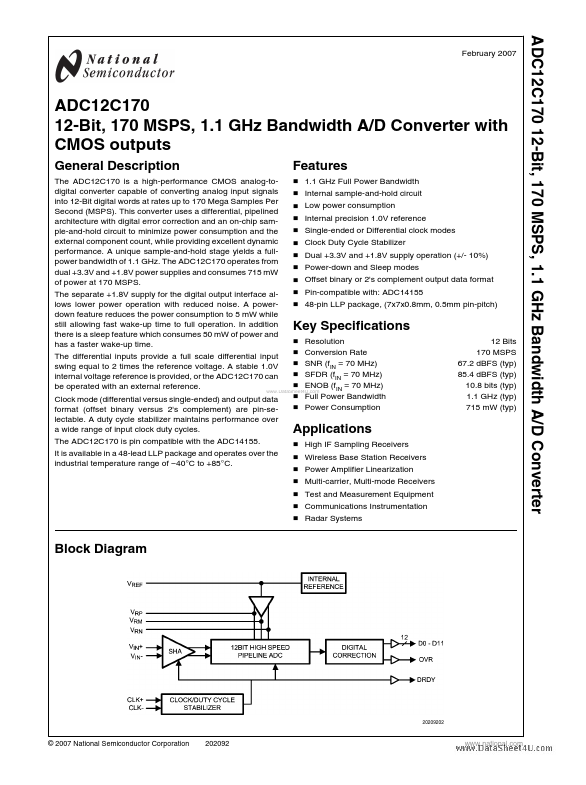

ADC12C170

Key Features

- 1.1 GHz Full Power Bandwidth digital converter capable of converting analog input signals

- Internal sample-and-hold circuit into 12-Bit digital words at rates up to 170 Mega Samples Per

- Low power consumption Second (MSPS). This converter uses a differential, pipelined

- Internal precision 1.0V reference architecture with digital error correction and an on-chip sam

- Single-ended or Differential clock modes ple-and-hold circuit to minimize power consumption and the external component count, while providing excellent dynamic

- Clock Duty Cycle Stabilizer performance. A unique sample-and-hold stage yields a full

- Dual +3.3V and +1.8V supply operation (+/- 10%) power bandwidth of 1.1 GHz. The ADC12C170 operates from

- Power-down and Sleep modes dual +3.3V and +1.8V power supplies and consumes 715 mW

- Offset binary or 2's complement output data format of power at 170 MSPS.

- Pin-compatible with: ADC14155 The separate +1.8V supply for the digital output interface allows lower power operation with reduced noise. A power