CGS64C800

CGS64C800 is Low Skew PLL 1-to-8 CMOS Clock Driver manufactured by National Semiconductor.

o

~National

~ Semiconductor

PRELIMINARY eecnn;)

I.:.l..o..o..

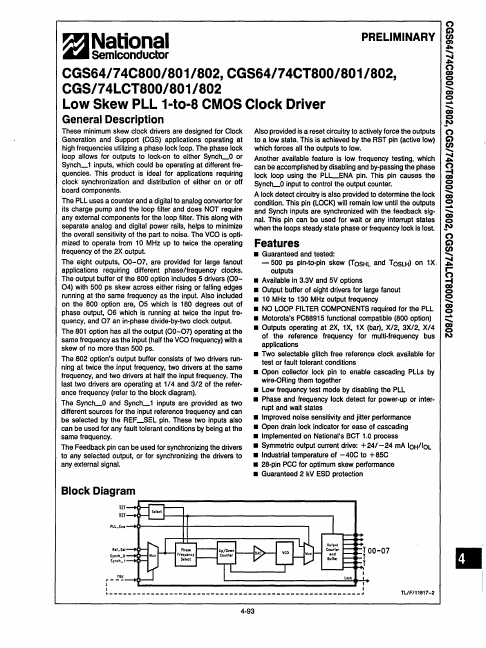

CGS64/74C800/801/802, CGS64/74CT800/801/802, o0I:loo

CD Q

CGS/74LCT800/801/802

Low Skew PLL 1-to-8 CMOS Clock Driver

.Q-......

General Description

,!')

These minimum skew clock drivers are designed for Clock Generation and Support (CGS) applications operating at high frequencies utilizing a phase lock loop. The phase lock loop allows for outputs to lock-on to either SyncLO or SyncL1 inputs, which could be operating at different frequencies. This product is ideal for applications requiring clock synchronization and distribution of either on or off board ponents.

The PLL uses a counter and a...