CLC016

Overview

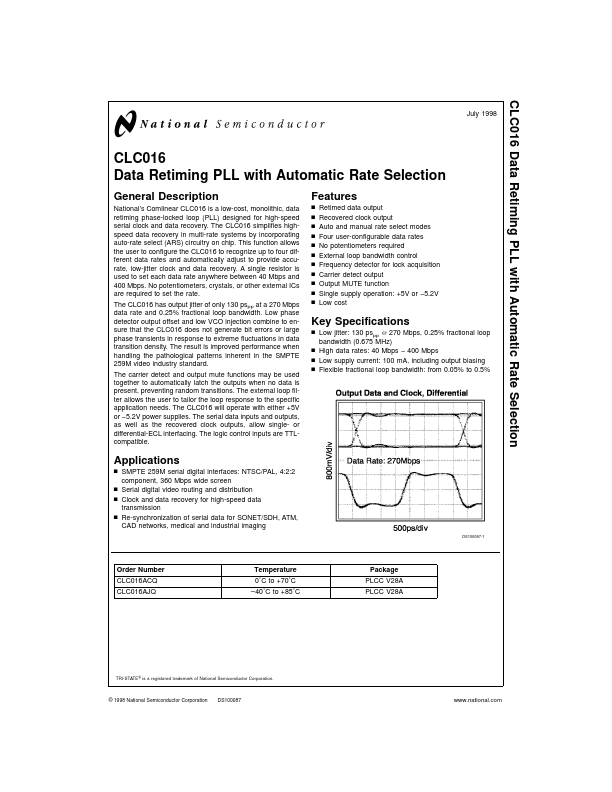

National’s Comlinear CLC016 is a low-cost, monolithic, data retiming phase-locked loop (PLL) designed for high-speed serial clock and data recovery. The CLC016 simplifies highspeed data recovery in multi-rate systems by incorporating auto-rate select (ARS) circuitry on chip.

- n n n n n n n n n

- Retimed data output Recovered clock output Auto and manual rate select modes Four user-configurable data rates No potentiometers required External loop bandwidth control Frequency detector for lock acquisition Carrier detect output Output MUTE function Single su