COP888CL

COP888CL is 8-Bit Microcontroller manufactured by National Semiconductor.

- Part of the COP888CL-XXX_N comparator family.

- Part of the COP888CL-XXX_N comparator family.

Description

The COP888 family of microcontrollers uses an 8-bit single chip core architecture fabricated with National Semiconductor’s M2CMOSTM process technology The COP888CL is a member of this expandable 8-bit core processor family of microcontrollers (Continued)

Packages 44 PLCC with 40 I O pins 40 DIP with 36 I O pins 28 DIP with 24 I O pins 28 SO with 24 I O pins

CPU Instruction Set Feature

Key Features

Two 16-bit timers each with two 16-bit registers supporting Processor Independent PWM mode External Event counter mode Input Capture mode 4 kbytes of on-chip ROM 128 bytes of on-chip RAM

Additional Peripheral Features

Idle Timer Multi-input Wake Up (MIWU) with optional interrupts (8) WATCHDOGTM and Clock Monitor logic MICROWIRE PLUSTM serial I O

1 ms instruction cycle time Ten multi-source vectored interrupts servicing External Interrupt with selectable edge Idle Timer T0 Timers (Each with 2 interrupts) MICROWIRE PLUS Multi-Input Wake Up Software Trap Default VIS (default interrupt) Versatile and easy to use instruction set 8-bit Stack Pointer (SP) stack in RAM Two 8-bit Register Indirect Data Memory Pointers (B X)

Fully Static CMOS

I O Features

Memory mapped I O Software selectable I O options (TRI-STATE Output Push-Pull Output Weak Pull-Up Input High Impedance Input) High current outputs Schmitt trigger inputs on port G

Low current drain (typically k 1 m A) Single supply operation 2 5V to 6 0V Temperature ranges 0 C to a 70 C b40 C to a 85 C b 55 C to a 125 C

Development Support

Emulation and OTP devices Real time emulation and full program debug offered by Meta Link Development System

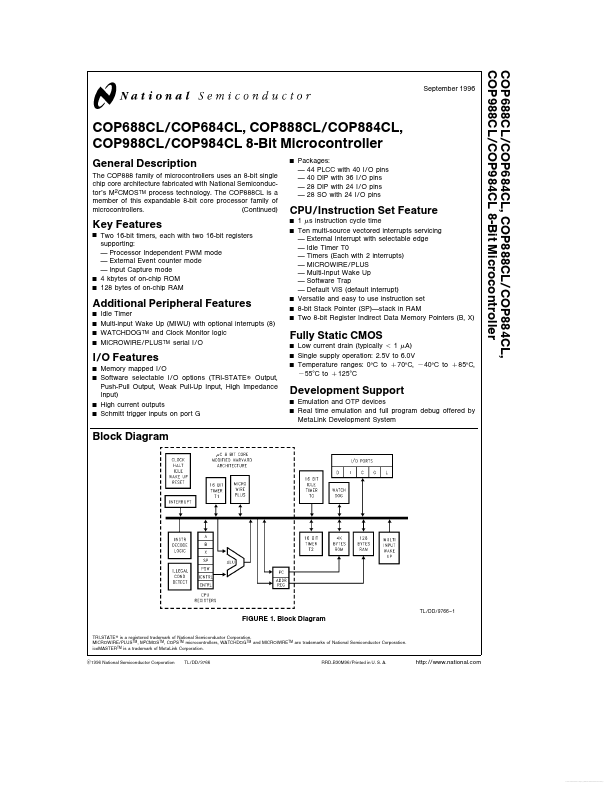

Block Diagram

TL DD 9766

- 1

FIGURE 1 Block Diagram

TRI-STATE is a registered trademark of National Semiconductor Corporation MICROWIRE PLUSTM M2CMOSTM COPSTM microcontrollers WATCHDOGTM and MICROWIRETM are trademarks of National Semiconductor Corporation ice MASTERTM is a trademark of Meta Link Corporation C1996...