DM54LS109A

DM54LS109A is Dual Positive-Edge-Triggered J-K Flip-Flops with Preset/ Clear/ and Complementar manufactured by National Semiconductor.

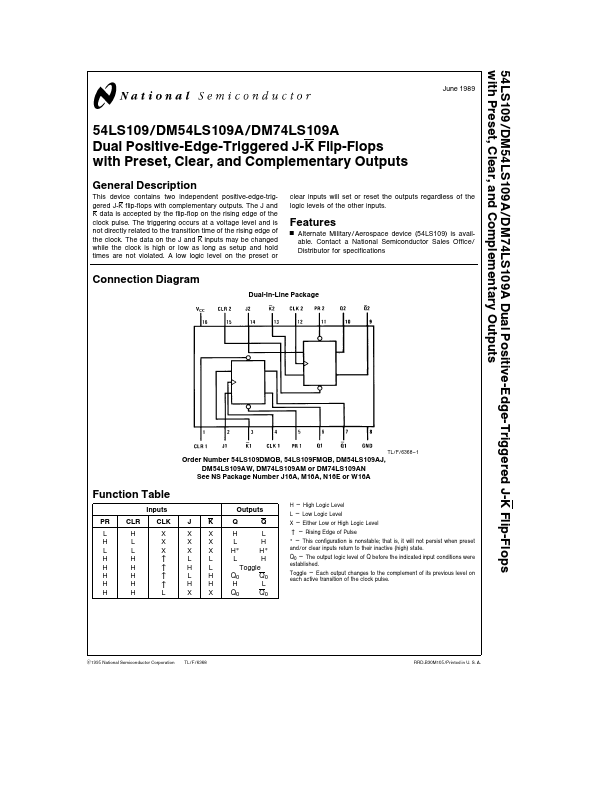

54LS109 DM54LS109A DM74LS109A Dual Positive-Edge-Triggered J-K Flip-Flops with Preset Clear and plementary Outputs

June 1989

54LS109 DM54LS109A DM74LS109A Dual Positive-Edge-Triggered J-K Flip-Flops with Preset Clear and plementary Outputs

General Description

This device contains two independent positive-edge-triggered J-K flip-flops with plementary outputs The J and K data is accepted by the flip-flop on the rising edge of the clock pulse The triggering occurs at a voltage level and is not directly related to the transition time of the rising edge of the clock The data on the J and K inputs may be changed while the clock is high or low as long as setup and hold times are not...