Description

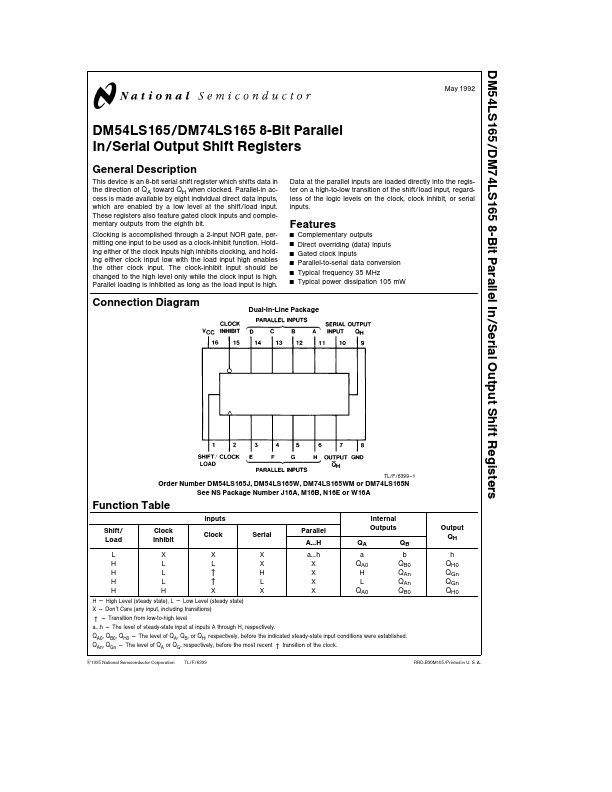

This device is an 8-bit serial shift register which shifts data in the direction of QA toward QH when clocked Parallel-in access is made available by eight individual direct data inputs which are enabled by a low level at the shift load input These registers also feature gated clock inputs and plementary outputs from the eighth bit Clocking is acplished through a 2-input NOR gate permitting one input to be used as a clock-inhibit function Holding either of the clock inputs high inhibits clocking and holding either clock input low with the load input high enables the other clock input The clock-inhibit input should be changed to the high level only while the clock input is high Parallel loading is inhibited as long as the load input is high Data at the parallel inputs are loaded directly into the register on a high-to-low transition of the shift load input regardless of the logic levels on the clock clock inhibit or serial inputs.