DM74125

Overview

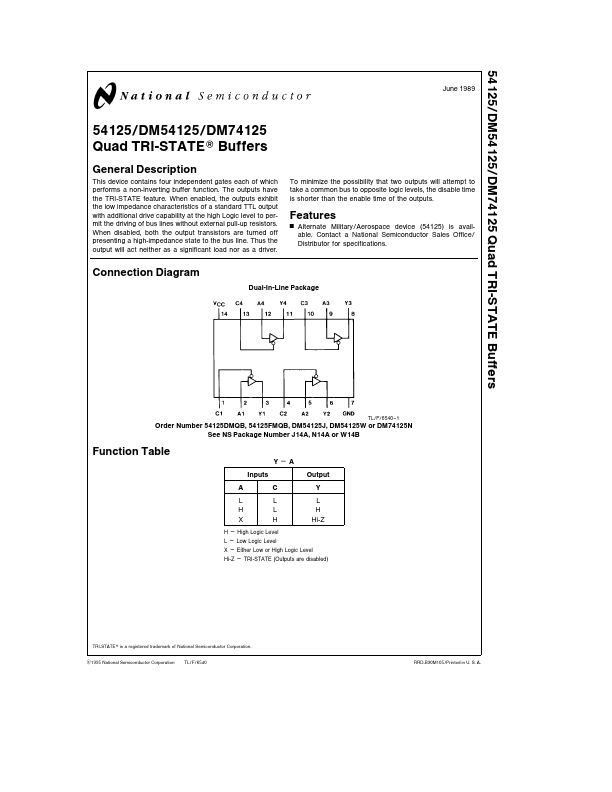

This device contains four independent gates each of which performs a non-inverting buffer function The outputs have the TRI-STATE feature When enabled the outputs exhibit the low impedance characteristics of a standard TTL output with additional drive capability at the high Logic level to permit the driving of bus lines without external pull-up resistors When disabled both the output transistors are turned off presenting a high-impedance state to the bus line Thus the output will act neither as a significant load nor as a driver To minimize the possibility that two outputs will attempt to take a common bus to opposite logic levels the disable time is shorter than the enable time of the outputs.