DM74S195 Overview

Description

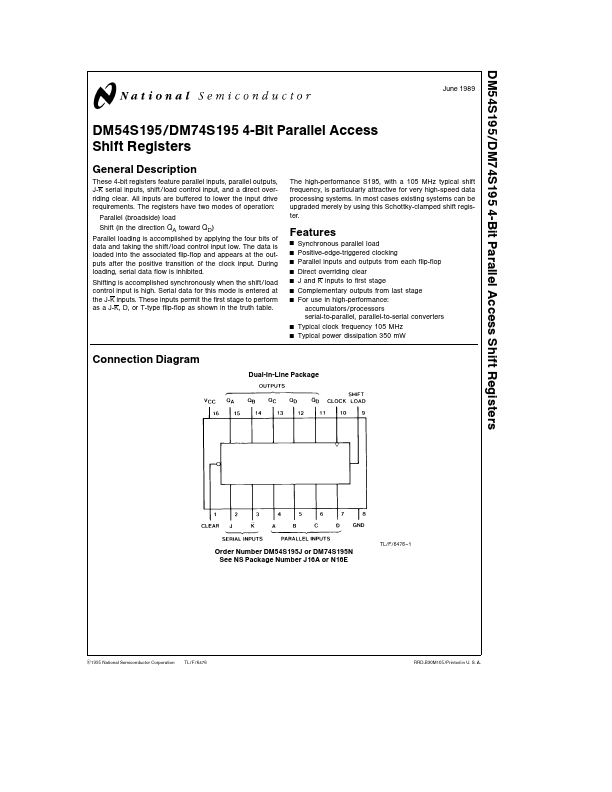

These 4-bit registers feature parallel inputs parallel outputs J-K serial inputs shift load control input and a direct overriding clear All inputs are buffered to lower the input drive requirements The registers have two modes of operation Parallel (broadside) load Shift (in the direction QA toward QD) Parallel loading is accomplished by applying the four bits of data and taking the shift load control input low The data is loaded into the associated flip-flop and appears at the outputs after the positive transition of the clock input During loading serial data flow is inhibited Shifting is accomplished synchronously when the shift load control input is high Serial data for this mode is entered at the J-K inputs These inputs permit the first stage to perform as a J-K D or T-type flip-flop as shown in the truth table The high-performance S195 with a 105 MHz typical shift frequency is particularly attractive for very high-speed data processing systems In most cases existing systems can be upgraded merely by using this Schottky-clamped shift register.