DP83815

DP83815 is 10/100 Mb/s Integrated PCI Ethernet Media Access Controller and Physical Layer manufactured by National Semiconductor.

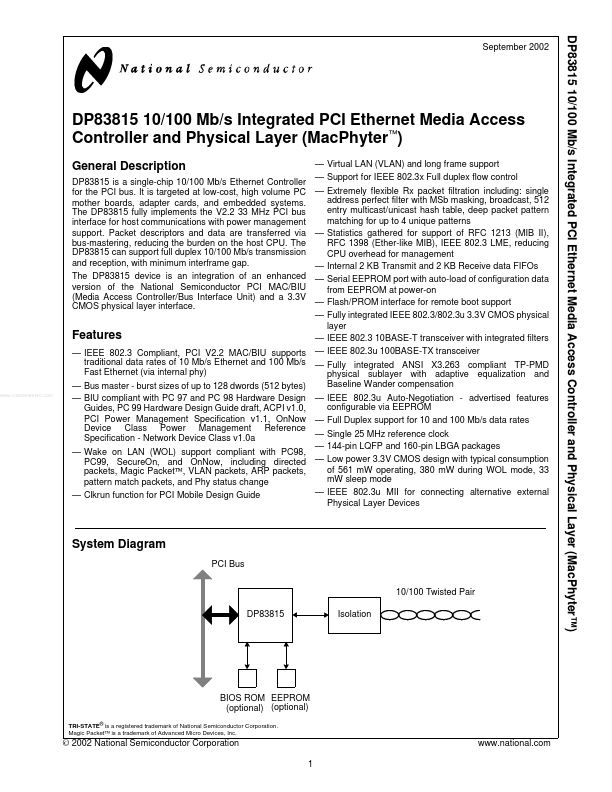

Description

- Virtual LAN (VLAN) and long frame support

- Support for IEEE 802.3x Full duplex flow control DP83815 is a single-chip 10/100 Mb/s Ethernet Controller for the PCI bus. It is targeted at low-cost, high volume PC

- Extremely flexible Rx packet filtration including: single address perfect filter with MSb masking, broadcast, 512 mother boards, adapter cards, and embedded systems. entry multicast/unicast hash table, deep packet pattern The DP83815 fully implements the V2.2 33 MHz PCI bus matching for up to 4 unique patterns interface for host munications with power management support. Packet descriptors and data are transferred via

- Statistics gathered for support of RFC 1213 (MIB II), bus-mastering, reducing the burden on the host CPU. The RFC 1398 (Ether-like MIB), IEEE 802.3 LME, reducing DP83815 can support full duplex 10/100 Mb/s transmission CPU overhead for management and reception, with minimum interframe gap.

- Internal 2 KB Transmit and 2 KB Receive data FIFOs The DP83815 device is an integration of an enhanced

- Serial EEPROM port with auto-load of configuration data version of the National Semiconductor PCI MAC/BIU from EEPROM at power-on (Media Access Controller/Bus Interface Unit) and a 3.3V

- Flash/PROM interface for remote boot support CMOS physical layer interface.

- Fully integrated IEEE 802.3/802.3u 3.3V CMOS physical layer Features

- IEEE 802.3 10BASE-T transceiver with integrated filters

- IEEE 802.3 pliant, PCI V2.2 MAC/BIU supports

- IEEE 802.3u 100BASE-TX transceiver traditional data rates of 10 Mb/s Ethernet and 100 Mb/s

- Fully integrated ANSI X3.263 pliant TP-PMD Fast Ethernet (via internal phy) physical sublayer with adaptive equalization and Baseline Wander pensation

- Bus master

- burst sizes of up to 128 dwords (512 bytes)

- BIU pliant with PC 97 and PC 98 Hardware Design

- IEEE 802.3u Auto-Negotiation

- advertised features configurable via EEPROM Guides, PC 99 Hardware Design Guide draft, ACPI v1.0, PCI Power Management...