DS64EV400

Description

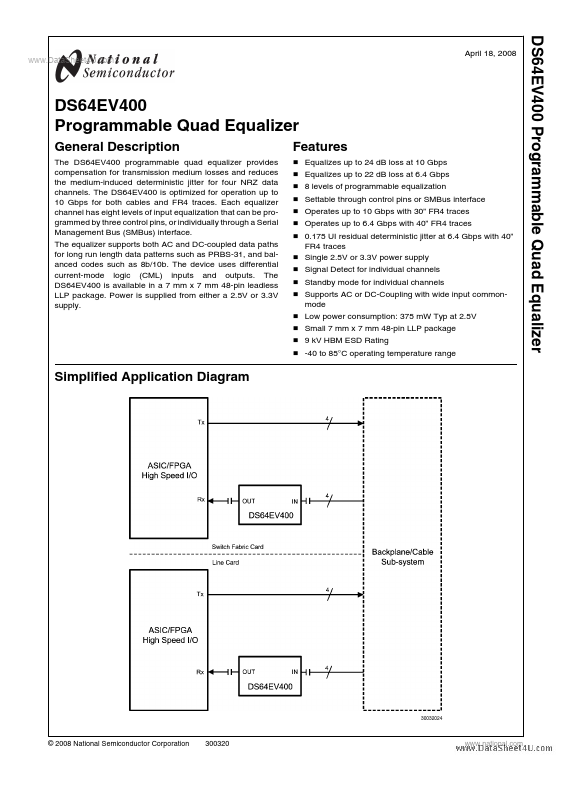

The DS64EV400 programmable quad equalizer provides pensation for transmission medium losses and reduces the medium-induced deterministic jitter for four NRZ data channels.

Key Features

- An on-chip 100Ω terminating resistor is connected between IN_0+ and IN_0

- Refer to Figure - Inverting and non-inverting CML differential inputs to the equalizer

- An on-chip 100Ω terminating resistor is connected between IN_1+ and IN_1

- Refer to Figure - Inverting and non-inverting CML differential inputs to the equalizer

- An on-chip 100Ω terminating resistor is connected between IN_2+ and IN_2

- Refer to Figure - Inverting and non-inverting CML differential inputs to the equalizer

- An on-chip 100Ω terminating resistor is connected between IN_3+ and IN_3

- Refer to Figure - Inverting and non-inverting CML differential outputs from the equalizer

- An on-chip 50Ω terminating resistor connects OUT_0+ to VDD and OUT_0- to VDD

- Inverting and non-inverting CML differential outputs from the equalizer