DS90C031B

Overview

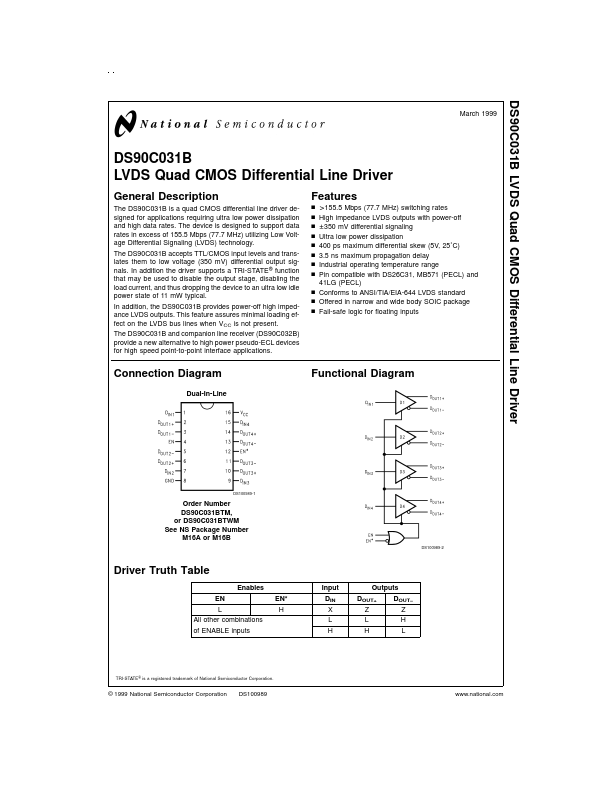

The DS90C031B is a quad CMOS differential line driver designed for applications requiring ultra low power dissipation and high data rates. The device is designed to support data rates in excess of 155.5 Mbps (77.7 MHz) utilizing Low Voltage Differential Signaling (LVDS) technology.

- n n n n n n n > 155.5 Mbps (77.7 MHz) switching rates High impedance LVDS outputs with power-off ± 350 mV differential signaling Ultra low power dissipation 400 ps maximum differential skew (5V, 25˚C) 3.5 ns maximum propagation delay Industrial operating temperature range Pin compatible with DS26C31, MB571 (PECL) and 41LG (PECL)

- Conforms to ANSI/TIA/EIA-644 LVDS standard

- Offered in narrow and wide body SOIC package

- Fail-safe logic for floating inputs Connection Diagram Dual-In-Line