DS90CR287

Overview

The DS90CR287 transmitter converts 28 bits of CMOS/TTL data into four LVDS (Low Voltage Differential Signaling) data streams. A phase-locked transmit clock is transmitted in parallel with the data streams over a fifth LVDS link.

- n n n n n n n n n n n

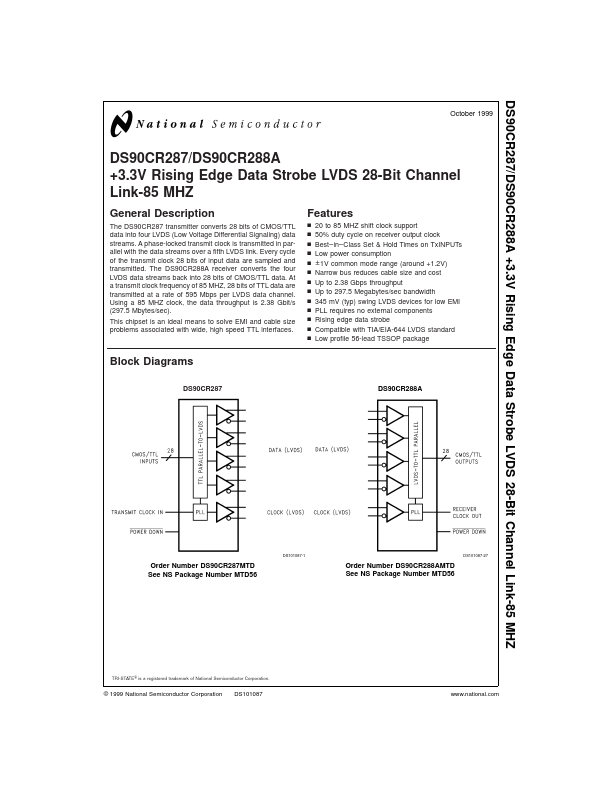

- 20 to 85 MHZ shift clock support 50% duty cycle on receiver output clock Best-in-Class Set & Hold Times on TxINPUTs Low power consumption ± 1V common mode range (around +1.2V) Narrow bus reduces cable size and cost Up to 2.38 Gbps throughput Up to 297.5 Megabytes/sec bandwidth 345 mV (typ) swing LVDS devices for low EMI PLL requires no external components Rising edge data strobe Compatible with TIA/EIA-644 LVDS standard Low profile 56-lead TSSOP package Block Diagrams