DS90LV048A

Description

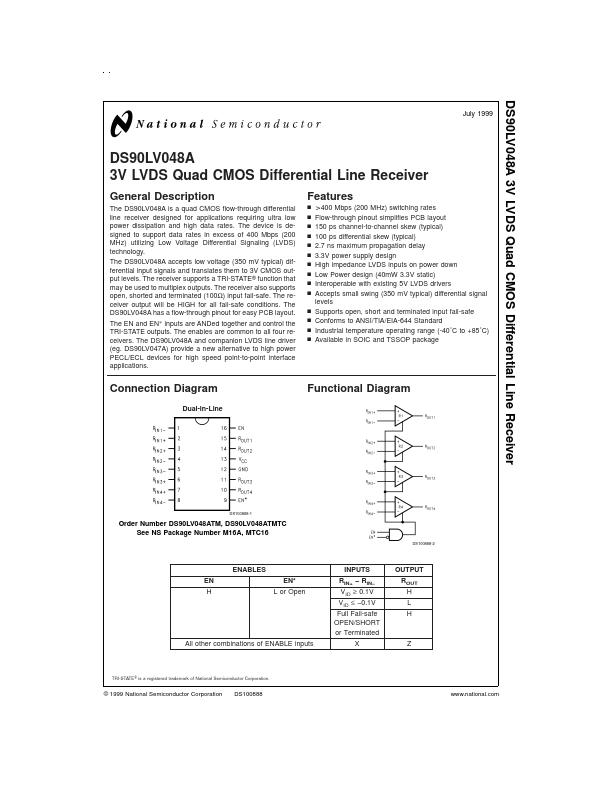

The DS90LV048A is a quad CMOS flow-through differential line receiver designed for applications requiring ultra low power dissipation and high data rates.

Key Features

- TRI-STATE ® is a registered trademark of National Semiconductor Corporation. © 1999 National Semiconductor Corporation DS100888 .national