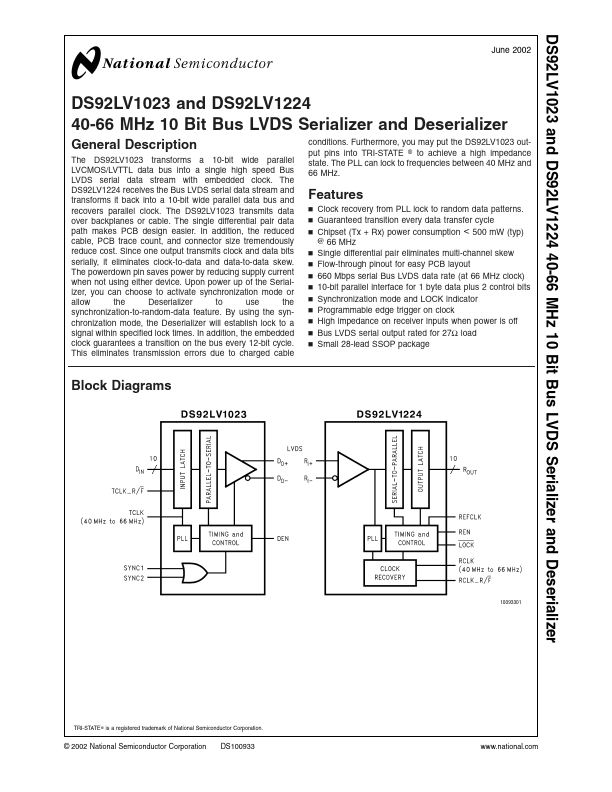

DS92LV1023

Description

The DS92LV1023 transforms a 10-bit wide parallel LVCMOS/LVTTL data bus into a single high speed Bus LVDS serial data stream with embedded clock.

Key Features

- n Clock recovery from PLL lock to random data patterns

- Guaranteed transition every data transfer cycle

- Chipset (Tx + Rx) power consumption < 500 mW (typ) @ 66 MHz

- Single differential pair eliminates multi-channel skew

- Synchronization mode and LOCK indicator

- Programmable edge trigger on clock

- High impedance on receiver inputs when power is off

- Bus LVDS serial output rated for 27Ω load

- Small 28-lead SSOP package