LM2507

LM2507 is Display interface Serializer/Deserializer manufactured by National Semiconductor.

Description

The LM2507 device adapts i80 CPU style display interfaces to the Mobile Pixel Link (MPL) Level zero serial link. When using smart CPU type interfaces, two chip selects support a main and sub display. A mode pin configures the device as a Master (MST) or Slave (SLV) so the same chip can be used on both sides of the interface. The interconnect is reduced from 21 signals to only 3 active signals with the LM2507 chipset easing flex interconnect design, size constraints and cost. The LM2507 in MST mode resides beside an application, graphics or baseband processor and translates a parallel bus from LVCMOS levels to serial Mobile Pixel Link levels for transmission over a flex cable (or coax) and PCB traces to the SLV located near the display module(s). When the Power_Down (PD- ) input is asserted on the Master, the MDn and MC line drivers are powered down to save current. The Slave is controlled by a separate Power_Down input. The LM2507 implements the physical layer of the MPL Level 0 Standard (MPL-0) and a 150 µA IB current (Class 0).

Features n CPU Display Interface support up to 800 x 300 1⁄2SVGA formats n Dual displays supported

- CS1- & CS2- n MPL-Level 0 Physical Layer using two data and one clock signal n Low Power Consumption n Pinout mirroring enables straight through layout with minimal vias n Level translation between host and display n Link power down mode reduces quiescent power under < 10 µA n 1.74V to 2.0V core / analog supply voltage range n 1.74V to 3.0V I/O supply voltage range

System Benefits n n n n Small Interface Low Power Low EMI Intrinsic Level Translation

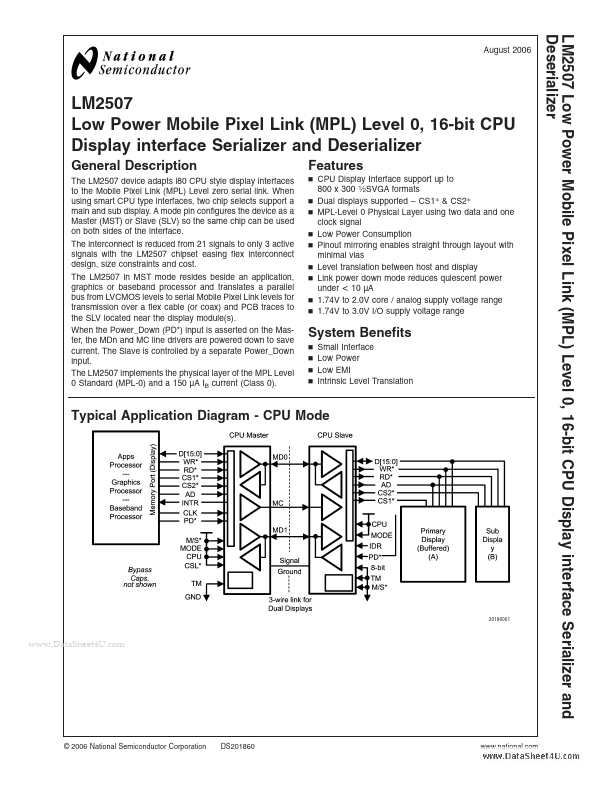

Typical Application Diagram

- CPU Mode

..

© 2006 National Semiconductor Corporation

DS201860

.national.

Pin Descriptions

- CPU

Description

Pin Name No. of Pins 2 1 I/O, Type CPU Master (MST) MPL Data Line Driver/Receiver MPL Clock Line Driver MPL Ground

- see Power/Ground Pins CPU mode configuration input Tie High Tie High for Master Tie Low for Slave CPU...