PC87415

PC87415 is PCI-IDE DMA Master Mode Interface Controller manufactured by National Semiconductor.

- Part of the PC8 comparator family.

- Part of the PC8 comparator family.

PC87415 PCI-IDE DMA Master Mode Interface Controller

PRELIMINARY

March 1996

PC87415 PCI-IDE DMA Master Mode Interface Controller

1 0 General Description

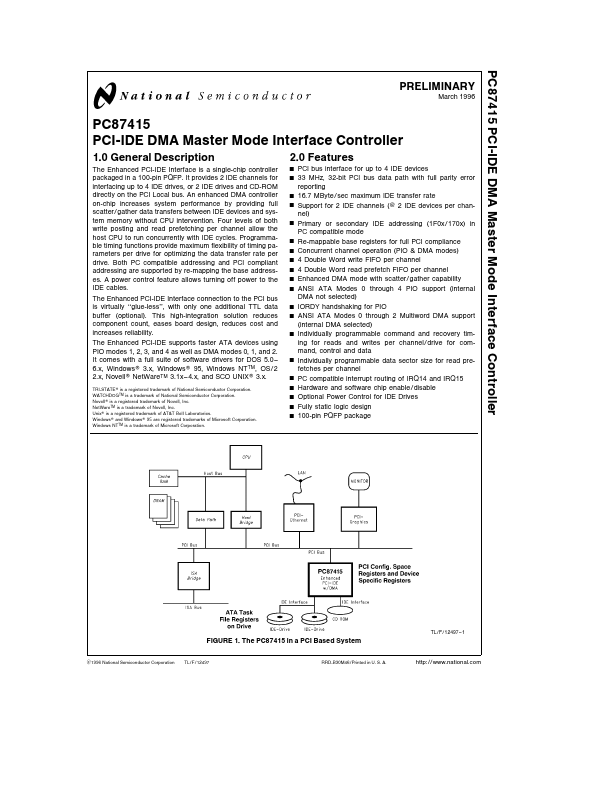

The Enhanced PCI-IDE Interface is a single-chip controller packaged in a 100-pin PQFP It provides 2 IDE channels for interfacing up to 4 IDE drives or 2 IDE drives and CD-ROM directly on the PCI Local bus An enhanced DMA controller on-chip increases system performance by providing full scatter gather data transfers between IDE devices and system memory without CPU intervention Four levels of both write posting and read prefetching per channel allow the host CPU to run concurrently with IDE cycles Programmable timing functions provide...