TP3057 Overview

Key Specifications

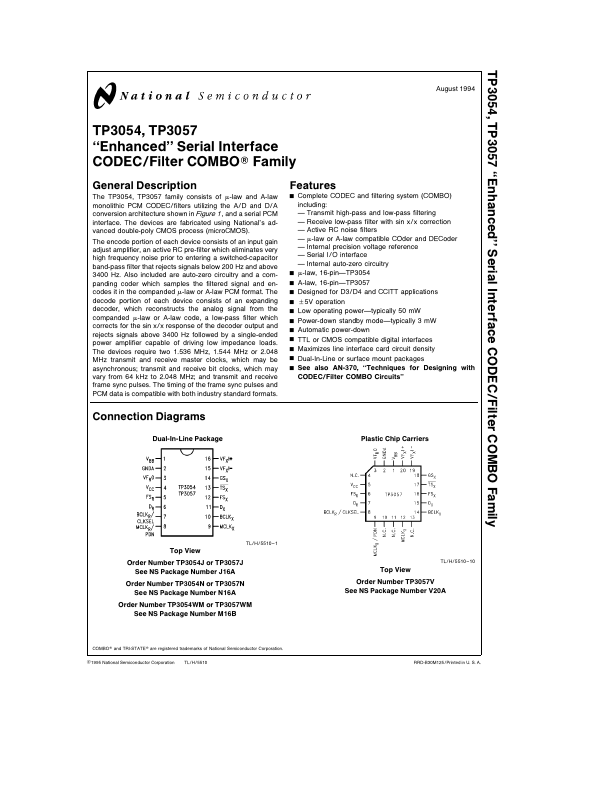

Package: PDIP

Mount Type: Through Hole

Pins: 16

Operating Voltage: 5 V

Description

The TP3054 TP3057 family consists of m-law and A-law monolithic PCM CODEC filters utilizing the A D and D A conversion architecture shown in Figure 1 and a serial PCM interface The devices are fabricated using National’s advanced double-poly CMOS process (microCMOS) The encode portion of each device consists of an input gain adjust amplifier an active RC pre-filter which eliminates very high frequency noise prior to entering a switched-capacitor band-pass filter that rejects signals below 200 Hz and above 3400 Hz Also included are auto-zero circuitry and a companding coder which samples the filtered signal and encodes it in the companded m-law or A-law PCM format The decode portion of each device consists of an expanding decoder which reconstructs the analog signal from the companded m-law or A-law code a low-pass filter which corrects for the sin x x response of the decoder output and rejects signals above 3400 Hz followed by a single-ended power amplifier capable of driving low impedance loads The devices require two 1 536 MHz 1 544 MHz or 2 048 MHz transmit and receive master clocks which may be asynchronous transmit and receive bit clocks which may vary from 64 kHz to 2 048 MHz and transmit and receive frame sync pulses The timing of the frame sync pulses and PCM data is compatible with both industry standard formats.