MM74HC76 Overview

Description

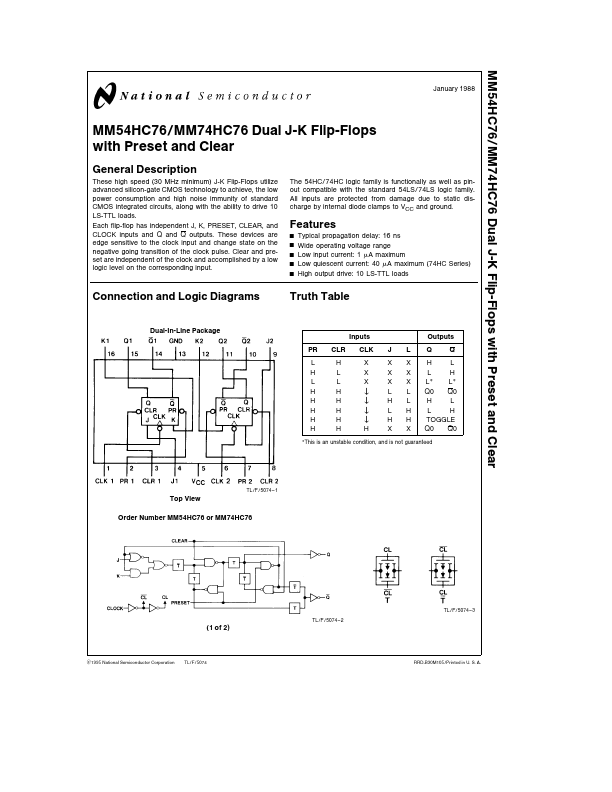

These high speed (30 MHz minimum) J-K Flip-Flops utilize advanced silicon-gate CMOS technology to achieve the low power consumption and high noise immunity of standard CMOS integrated circuits along with the ability to drive 10 LS-TTL loads Each flip-flop has independent J K PRESET CLEAR and CLOCK inputs and Q and Q outputs These devices are edge sensitive to the clock input and change state on the negative going transition of the clock pulse Clear and preset are independent of the clock and accomplished by a low logic level on the corresponding input The 54HC 74HC logic family is functionally as well as pinout compatible with the standard 54LS 74LS logic family All inputs are protected from damage due to static discharge by internal diode clamps to VCC and ground.

Key Features

- C1995 National Semiconductor Corporation TL F 5074 RRD-B30M105 Printed in U S A