54F413

54F413 is 64 x 4 First-In First-Out Buffer Memory manufactured by National Semiconductor.

Description

The ’F413 is an expandable fall-through type high-speed First-In First-Out (FIFO) buffer memory organized as 64 words by four bits The 4-bit input and output registers record and transmit respectively asynchronous data in parallel form Control pins on the input and output allow for handshaking and expansion The 4-bit wide 62-bit deep fallthrough stack has self-contained control logic

Features

Y Separate input and output clocks Y Parallel input and output Y Expandable without external logic Y 15 MHz data rate Y Supply current 160 m A max Y Available in SOIC (300 mil only) mercial 74F413PC

Military 54F413DM (Note 1)

Package Number

N16E

J16A

Package Description

16-Lead (0 300 Wide) Molded Dual-In-Line 16-Lead Ceramic Dual-In-Line

Note 1 Military grade device with environmental and burn-in processing Use suffix e DMQB

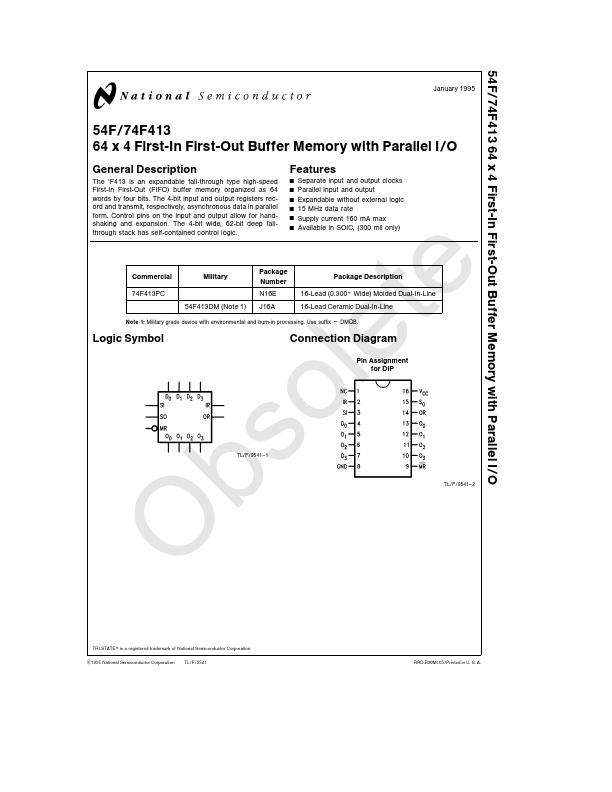

Logic Symbol

Connection Diagram

Pin Assignment for DIP

TL F 9541

- 1

TL F 9541

- 2

TRI-STATE is a registered trademark of National Semiconductor Corporation C1995 National Semiconductor Corporation TL F 9541

RRD-B30M105 Printed in U S A

Unit Loading Fan Out

Pin Names

D0

- D3 O0

- O3 IR SI SO OR MR

Description

Data Inputs Data Outputs Input Ready Shift In Shift Out Output Ready Master Reset

54F 74F

UL HIGH LOW

1 0 0 667 50 13 3 1 0 0 667 1 0 0 667 1 0 0 667 1 0 0 667 1 0 0 667

Input IIH IIL Output IOH IOL

20 m A b0 4 m A b1 m A 8 m A

20 m A b0 4 m A 20 m A b0 4 m A 20 m A b0 4 m A 20 m A b0 4 m A 20 m A b0 4 m A

Functional Description

Data Input Data is entered into the FIFO on D0

- D3 inputs To enter data the Input Ready (IR) should be HIGH indicating that the first location is ready to accept data Data then present at the four data inputs is entered into the first location when the Shift In (SI) is brought HIGH An SI HIGH signal causes the IR to go LOW Data remains at the first location until SI is brought LOW When SI is brought LOW and the FIFO is not full IR will go HIGH indicating that more room is available Simultaneously data will...