54F521

54F521 is 8-Bit Identity Comparator manufactured by National Semiconductor.

Description

The ’F521 is an expandable 8-bit parator It pares two words of up to eight bits each and provides a LOW output when the two words match bit for bit The expansion input IA e B also serves as an active LOW enable input

Features

Y Y Y pares two 8-bit words in 6 5 ns typ Expandable to any word length 20-pin package mercial 74F521PC

Military

Package Number N20A

Package Description

20-Lead (0 300 Wide) Molded Dual-In-Line 20-Lead Ceramic Dual-In-Line 20-Lead (0 300 Wide) Molded Small Outline JEDEC 20-Lead (0 300 Wide) Molded Small Outline EIAJ 20-Lead Molded Shrink Small Outline EIAJ type II

54F521DM (Note 2) 74F521SC (Note 1) 74F521SJ (Note 1) 74F521MSA (Note 1)

J20A M20B M20D MSA20

Note 1 Devices also available in 13 reel Use suffix e SCX SJX and MSAX Note 2 Military grade device with environmental and burn-in processing Use suffix e DMQB

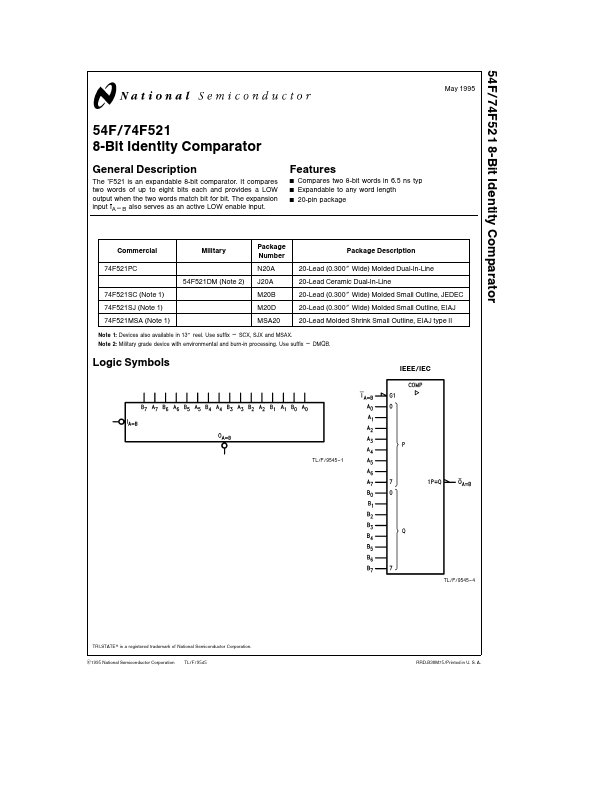

Logic Symbols

IEEE IEC

TL F 9545

- 1

TL F 9545

- 4

TRI-STATE is a registered trademark of National Semiconductor Corporation C1995 National Semiconductor Corporation

TL F 9545

RRD-B30M75 Printed in U S A

Unit Loading Fan Out

54F 74F Pin Names Description

UL HIGH LOW 10 10 10 10 10 10 50 33 3 Input IIH IIL Output IOH IOL 20 m A b0 6 m A 20 m A b0 6 m A 20 m A b0 6 m A b 1 m A 20 m A

A 0

- A7 B 0

- B7 IA e B OA e B

Word A Inputs Word B Inputs Expansion or Enable Input (Active LOW) Identity Output (Active LOW)

Truth Table

Inputs IA e B L L H H A B Ae B Ai B Ae B Ai B Output OA e B L H H H

H e HIGH Voltage Level L e LOW Voltage Level A0 e B0 A1 e B1 A2 e B2 etc

Connection Diagrams

Pin Assignment for DIP SOIC SSOP and Flatpak

Logic Diagram

TL F 9545- 2

Pin Assignment for LCC

TL F 9545

- 5

Please note that this diagram is provided only for the understanding of logic operations and should not be used to estimate propagation delays

TL F 9545-...