54LS109

54LS109 is Dual Positive-Edge-Triggered J-K Flip-Flops manufactured by National Semiconductor.

Description

This device contains two independent positive-edge-triggered J-K flip-flops with plementary outputs The J and K data is accepted by the flip-flop on the rising edge of the clock pulse The triggering occurs at a voltage level and is not directly related to the transition time of the rising edge of the clock The data on the J and K inputs may be changed while the clock is high or low as long as setup and hold times are not violated A low logic level on the preset or clear inputs will set or reset the outputs regardless of the logic levels of the other inputs

Features

Y Alternate Military Aerospace device (54LS109) is available Contact a National Semiconductor Sales Office Distributor for specifications

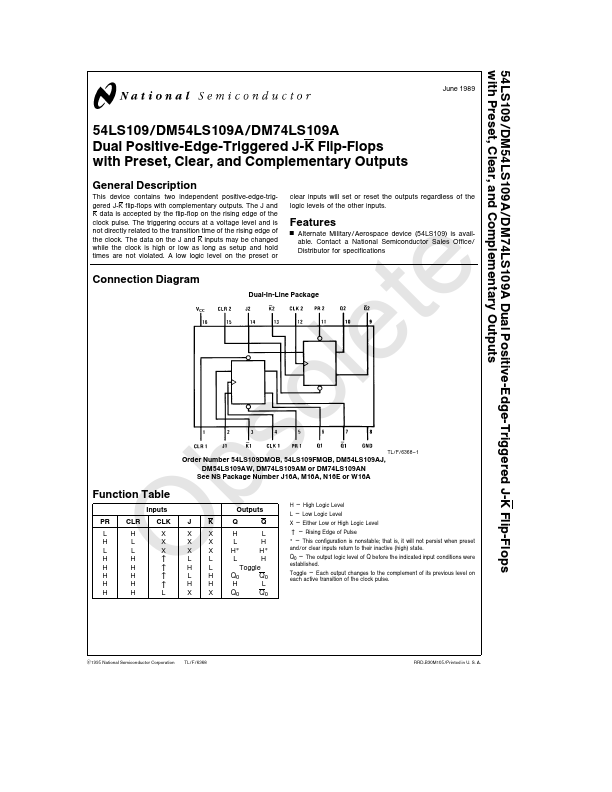

Connection Diagram

Dual-In-Line Package

TL F 6368

- 1

Order Number 54LS109DMQB 54LS109FMQB DM54LS109AJ DM54LS109AW DM74LS109AM or DM74LS109AN

See NS Package Number J16A M16A N16E or W16A

Function Table

Inputs

Outputs

PR CLR CLK J K

X XX H

H H u LL L H

H H u HL

Toggle u H H

L H Q0

Q0

H H u HH H L

X X Q0

Q0

H e High Logic...