74ACT823

74ACT823 is 9-Bit D Flip-Flop manufactured by National Semiconductor.

Description

The ’ACT823 is a 9-bit buffered register It features

Clock Enable and Clear which are ideal for parity bus interfacing in high performance microprogramming systems The ’ACT823 offers noninverting outputs and is fully patible with AMD’s Am29823

Features

Outputs source sink 24 m A TRI-STATE outputs for bus interfacing Inputs and outputs are on opposite sides ’ACT823 has TTL-patible inputs

..

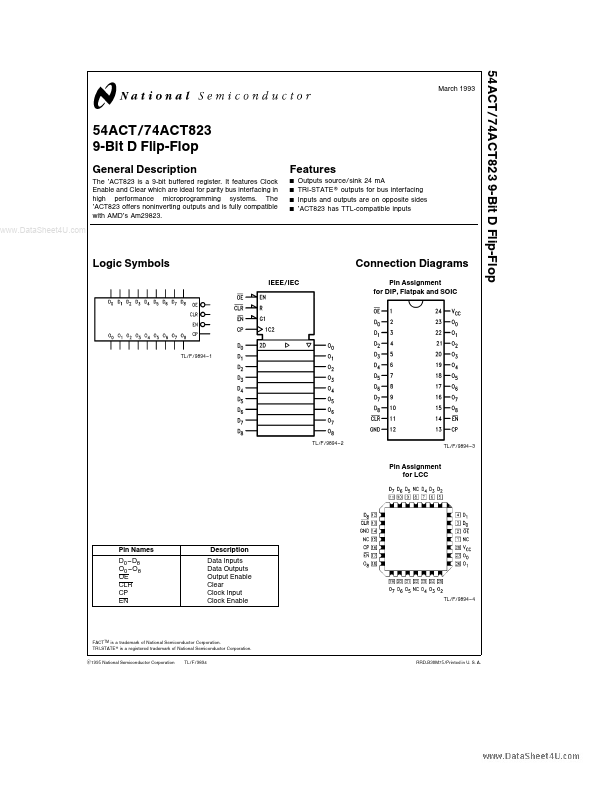

Logic Symbols

IEEE IEC

Connection Diagrams

Pin Assignment for DIP Flatpak and SOIC

TL F 9894- 1

TL F 9894

- 2

TL F 9894

- 3

Pin Assignment for LCC

Pin Names D0

- D8 O0

- O8 OE CLR CP EN

Description

Data Inputs Data Outputs Output Enable Clear Clock Input Clock Enable

TL F 9894

- 4

FACTTM is a trademark of National Semiconductor Corporation TRI-STATE is a registered trademark of National Semiconductor Corporation C1995 National Semiconductor Corporation TL F 9894 RRD-B30M75 Printed in U S A

Functional Description

The ’ACT823 consists of nine D-type edge-triggered flipflops These have TRI-STATE outputs for bus systems organized with inputs and outputs on opposite sides The buffered clock (CP) and buffered Output Enable (OE) are mon to all flip-flops The flip-flops will store the state of their individual D inputs that meet the setup and hold time requirements on the LOW-to-HIGH CP transition With OE LOW the contents of the flip-flops are available at the outputs When OE is HIGH the outputs go to the high impedance state Operation of the OE input does not affect Function Table Inputs OE CLR X X L L H H H H H H EN L L X X H H L L L L CP L L X X X X L L L L D L H X X X X L H L H Internal Q L H L L NC NC L H L H Output O Z Z Z L Z NC Z Z L H High Z High Z Clear Clear Hold Hold Load Load Load Load Function the state of the flip-flops In addition to the Clock and Output Enable pins there are Clear (CLR) and Clock Enable (EN) pins These devices are ideal for parity bus interfacing in high performance systems When CLR is LOW and OE is LOW the outputs are LOW...