CGS100P2531

CGS100P2531 is PECl-TTl 2 to 10 Minimum Skew Clock Driver manufactured by National Semiconductor.

- Part of the CGS100P2530 comparator family.

- Part of the CGS100P2530 comparator family.

Description

Features

.C..A..l

These minimum skew clock drivers are designed for Clock ~ PECL-TTL version of National's CGS7482528 TTL

Generation & Support (CGS) applications, particularly for clock drivers

ECL to TTL clock tree distribution schemes. The '2530 and

- Clock Generation & Support (CGS) devices ideal for

'2531 are single supply devices with guaranteed minimum

ECL and TTL clock trees with CGS 100311 output skew across the outputs of a given device. Skew parameters are also provided as a means to measure duty cycle requirements as those found in high speed clocking systems. The '2530 is a minimum skew clock driver with one input driving ten outputs and the '2531 is a selectable two input to 10 outputs, specifically designed for signal generation and clock distribution applications.

- 1-to-10 or 2-to-10 low skew clock distribution

- 550 ps pin-to-pin output skew

- Specification for transition skew to meet duty cycle re- quirements

- 28-pin PCC to minimize high speed switching noise and for low dynamic power consumption

- Current sourcing 48 rn A and current sinking of 64 rn A

- Low dynamic power consumption above 20 MHz

- Guaranteed 4 k V ESD protection

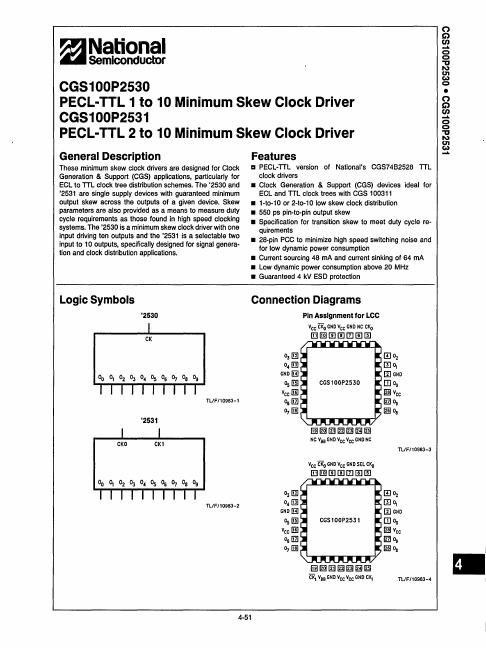

Logic Symbols

'2530

'2531 e KO

Connection Diagrams

Pin Assignment for LCC vee CKQ e ND Vee e ND NC CKo

II] [QJ [!] [!][I! [!] l ID

TUF/l0983-1

°3@

°4 I!] e ND Ii]

Os Ii]! Vee @ 0&1il I ,?Ii]] m rna0,2 me ND moo

~ Vee

Ill! 09

~08

(ij JRQJIIi I- Irn~~ NC Vaa e ND Vee Vee e ND Ne

Vee CKQ e ND Vee e ND SEL CKo 1I][QJ[!]m[IJ[!]l ID

TL/F/l0983-3

TL/F/l0983-2

°3@

°4 I!] e ND Ii]

Os Ii]!

Vee@

O&1il I ,?Ii]] m rna0,2 me ND moo

~...