CGS410

CGS410 is Programmable Clock Generator manufactured by National Semiconductor.

Description

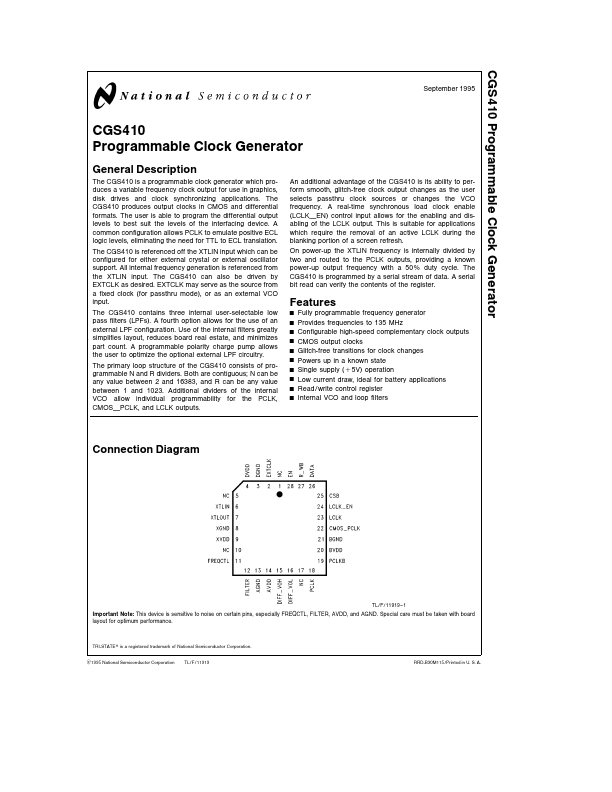

The CGS410 is a programmable clock generator which produces a variable frequency clock output for use in graphics disk drives and clock synchronizing applications The CGS410 produces output clocks in CMOS and differential formats The user is able to program the differential output levels to best suit the levels of the interfacing device A mon configuration allows PCLK to emulate positive ECL logic levels eliminating the need for TTL to ECL translation The CGS410 is referenced off the XTLIN input which can be configured for either external crystal or external oscillator support All internal frequency generation is referenced from the XTLIN input The CGS410 can also be driven by EXTCLK as desired EXTCLK may serve as the source from a fixed clock (for passthru mode) or as an external VCO input The CGS410 contains three internal user-selectable low pass filters (LPFs) A fourth option allows for the use of an external LPF configuration Use of the internal filters greatly simplifies layout reduces board real estate and minimizes part count A programmable polarity charge pump allows the user to optimize the optional external LPF circuitry The primary loop structure of the CGS410 consists of programmable N and R dividers Both are contiguous N can be any value between 2 and 16383 and R can be any value between 1 and 1023 Additional dividers of the internal VCO allow individual programmability for the PCLK CMOS PCLK and LCLK outputs An additional advantage of the CGS410 is its ability to perform smooth glitch-free clock output changes as the user selects passthru clock sources or changes the VCO frequency A real-time synchronous load clock enable (LCLK EN) control input allows for the enabling and disabling of the LCLK output This is suitable for applications which require the removal of an active LCLK during the blanking portion of a screen refresh On power-up the XTLIN frequency is internally divided by two and routed to the PCLK outputs providing a known...