DP83902A

DP83902A is ST-NICTM Serial Network Interface Controller for Twisted Pair manufactured by National Semiconductor.

Description

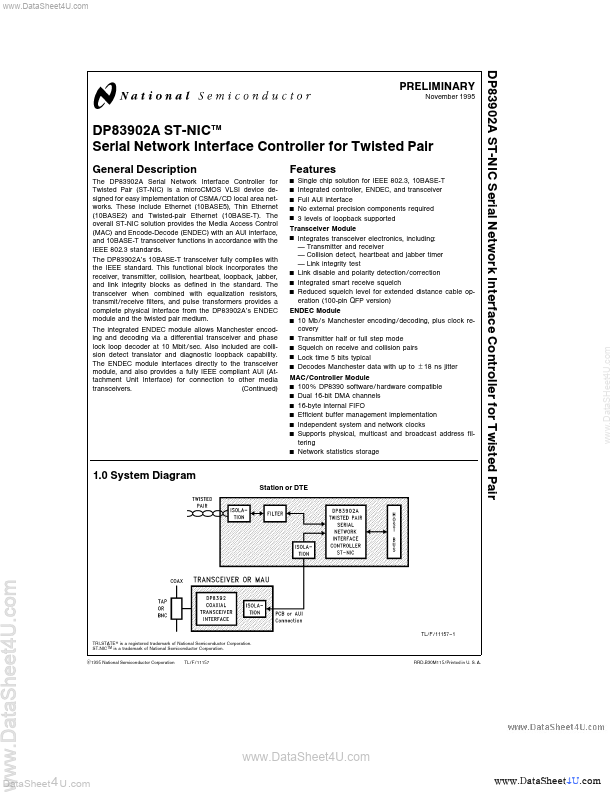

The DP83902A Serial Network Interface Controller for Twisted Pair (ST-NIC) is a micro CMOS VLSI device designed for easy implementation of CSMA CD local area networks These include Ethernet (10BASE5) Thin Ethernet (10BASE2) and Twisted-pair Ethernet (10BASE-T) The overall ST-NIC solution provides the Media Access Control (MAC) and Encode-Decode (ENDEC) with an AUI interface and 10BASE-T transceiver functions in accordance with the IEEE 802 3 standards The DP83902A’s 10BASE-T transceiver fully plies with the IEEE standard This functional block incorporates the receiver transmitter collision heartbeat loopback jabber and link integrity blocks as defined in the standard The transceiver when bined with equalization resistors transmit receive filters and pulse transformers provides a plete physical interface from the DP83902A’s ENDEC module and the twisted pair medium The integrated ENDEC module allows Manchester encoding and decoding via a differential transceiver and phase lock loop decoder at 10 Mbit sec Also included are collision detect translator and diagnostic loopback capability The ENDEC module interfaces directly to the transceiver module and also provides a fully IEEE pliant AUI (Attachment Unit Interface) for connection to other media transceivers (Continued)

Features

Single chip solution for IEEE 802 3 10BASE-T Integrated controller ENDEC and transceiver Y Full AUI interface Y No external precision ponents required Y 3 levels of loopback supported Transceiver Module Y Integrates transceiver electronics including Transmitter and receiver Collision detect heartbeat and jabber timer Link integrity test Y Link disable and polarity detection correction Y Integrated smart receive squelch Y Reduced squelch level for extended distance cable operation (100-pin QFP version) ENDEC Module Y 10 Mb s Manchester encoding decoding plus clock recovery Y Transmitter half or full step mode Y Squelch on receive and collision pairs Y Lock time 5 bits typical Y...