DS25MB200

DS25MB200 is Dual 2.5 Gbps 2:1/1:2 CML Mux/Buffer manufactured by National Semiconductor.

Description

The DS25MB200 is a dual signal conditioning 2:1 multiplexer and 1:2 fan-out buffer designed for use in backplane redundancy applications. Signal conditioning features include input equalization and programmable output pre-emphasis that enable data munication in FR4 backplanes up to 2.5 Gbps. Each input stage has a fixed equalizer to reduce ISI distortion from board traces. All output drivers have 4 selectable steps .. of pre-emphasis to pensate for transmission losses from long FR4 backplanes and reduce deterministic jitter. The preemphasis levels can be independently controlled for the lineside and switch-side drivers. The internal loopback paths from switch-side input to switch-side output enable at-speed system testing. All receiver inputs are internally terminated with 100Ω differential terminating resistors. All drivers are internally terminated with 50Ω to VCC.

Features

- -

- -

- -

- -

- 0.6- 2.5 Gbps low jitter operation Fixed input equalization Programmable output pre-emphasis Independent switch and line side pre-emphasis controls Programmable switch-side loopback modes On-chip terminations HBM ESD rating 6 k V on all pins +3.3V supply Lead-less LLP-48 package (7mm x 7mm x 0.8mm, 0.5mm pitch)

- - 40°C to +85°C operating temperature range

Applications

- Backplane or cable driver

- Redundancy and signal conditioning applications

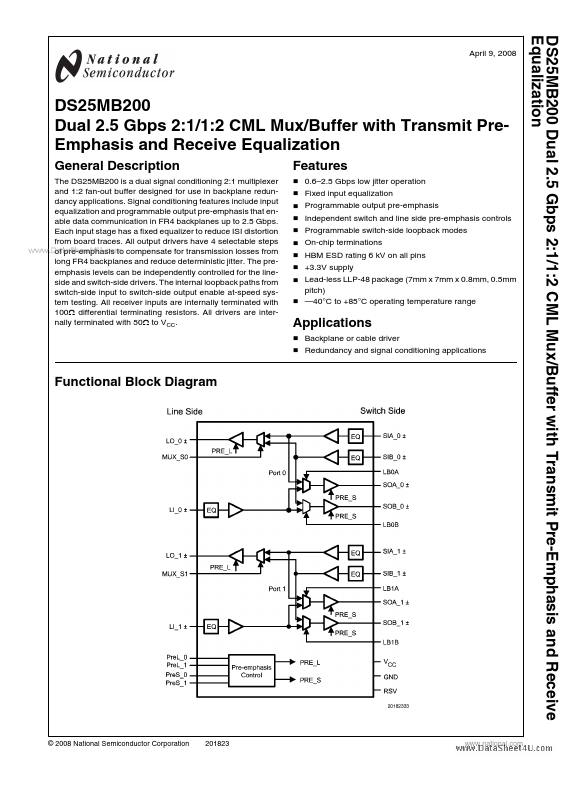

Functional Block Diagram

© 2008 National Semiconductor Corporation

.national.

Simplified Block Diagram

..

.national.

Connection Diagram

..

Order Number DS25MB200TSQ See NS Package Number NSQAV48

.national.

Pin Descriptions

Pin Name LI_0+ LI_0- LO_0+ LO_0- LI_1+ LI_1- LO_1+ LO_1- SOA_0+ SOA_0- Pin Number 6 7 33 34 30 31 9 10 46 45 4 3 40 39 43 42 22 21 28 27 16 15 19 18 37 13 12 1 36 25 47 48 23 24 26 I/O I O I O Description

Inverting and non-inverting differential inputs of port_0 at the line side. LI_0+ and LI_0- have an internal 50Ω...