INS1671

INS1671 is Asynchronous/Synchronous Transmitter/Receiver manufactured by National Semiconductor.

Description

The INS1671 is a programmable Asynchronous/Synchronous Transmitter/Receiver (ASTRa) chip housed' in a standard, 40-pin dual-in-line package. The chip, which is fabricated using N-channel silicon gate Ma S technology, provides a serial data input/output interface in a busstructured system. The chip is capable of full duplex operation with synchronous or asynchronous data munications systems.

The INS1671 is designed to operate on a multiplexed, bidirectional bus with other bus-oriented devices. The functional configuration of the INS1671 is programmed by the system software via the bus and all parallel data transfers within the system are acplished over the bus lines. In addition, the INS1671 contains a provision for hardwiring a unique 5-bit identification code to a chip, thereby allowing up to 32 INS1671 devices to be addressed via the multiplexed bus.

Features

- Synchronous and Asynchronous Full Duplex Operations

- Synchronous Mode Capabilities

- Selectable 5- to 8-Bit C'haracters

- T.wo Contiguous SYN Characters Provide Synchronization Programmable SYN and DLE Characters Stripping Programmable SYN and SYN-DLE Characters Insertion

- Asynchronous Mode Capabilities

- Selectable 5- to 8-Bit Characters Line Break Detection

- 1-,1%-, or 2-Stop Bit Detection

- False Start Bit Detection

- Automatic Serial Echo Mode

- DC to 1M Baud Rate

- 8 Selectable Clock Rates (4 Programmable)

- Transmission Error Detection Capabilities

- Parity

- Overrun

- Framing

- Double Buffering of Data

- 8-Bit Bidirectional Bus for Data, Status, and Control

Words

- All Inputs and Outputs TTL patible

- On-Line Diagnostic Mode'

- Reduces System ponent Count

- Direct Plug-In Replacement for Western Digital FD1671

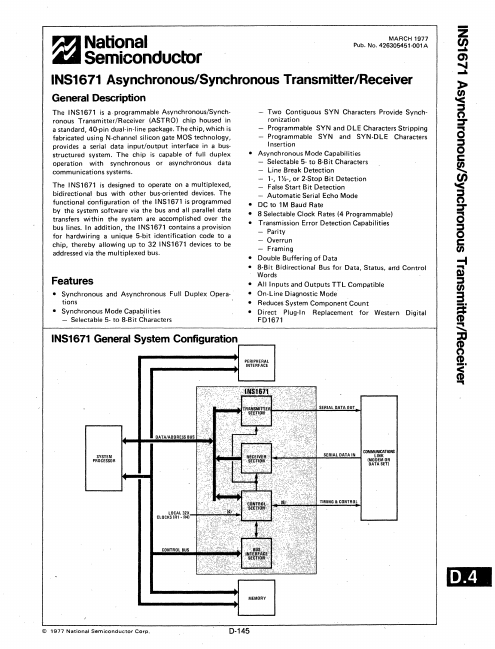

INS1671 General System Configuration..---_....,

PERIPHERAL INTERf ACE

SERIAL DATA OUT

SYSTEM PROCESSOR

CLOCKl S O(RC1 A- Rl4)32Xi""1~~;;!f4~~~

CONTROL BUS

© 1977 National Semiconductor Corp.

MEMORY

0- 145

SERIAL DATA IN

MUNICATIONS LINK

(MODEM OR DATASET)

TIMING &...