SCAN182245A

SCAN182245A is Non-Inverting Transceiver manufactured by National Semiconductor.

Description

The SCAN182245A is a high performance Bi CMOS bidirectional line driver featuring separate data inputs organized into dual 9-bit bytes with byte-oriented output enable and direction control signals This device is pliant with IEEE 1149 1 Standard Test Access Port and Boundary Scan Architecture with the incorporation of the defined boundary-scan test logic and test access port consisting of Test Data Input (TDI) Test Data Out (TDO) Test Mode Select (TMS) and Test Clock (TCK)

Features

Y Y Y Y Y Y

High performance Bi CMOS technology 25X series resistors in outputs eliminate the need for external terminating resistors Dual output enable control signals TRI-STATE outputs for bus-oriented applications 25 mil pitch SSOP (Shrink Small Outline Package) IEEE 1149 1 (JTAG) pliant Includes CLAMP IDCODE and HIGHZ instructions Additional instructions SAMPLE-IN SAMPLE-OUT and EXTEST-OUT Power Up TRI-STATE for hot insert Member of National’s SCAN Products

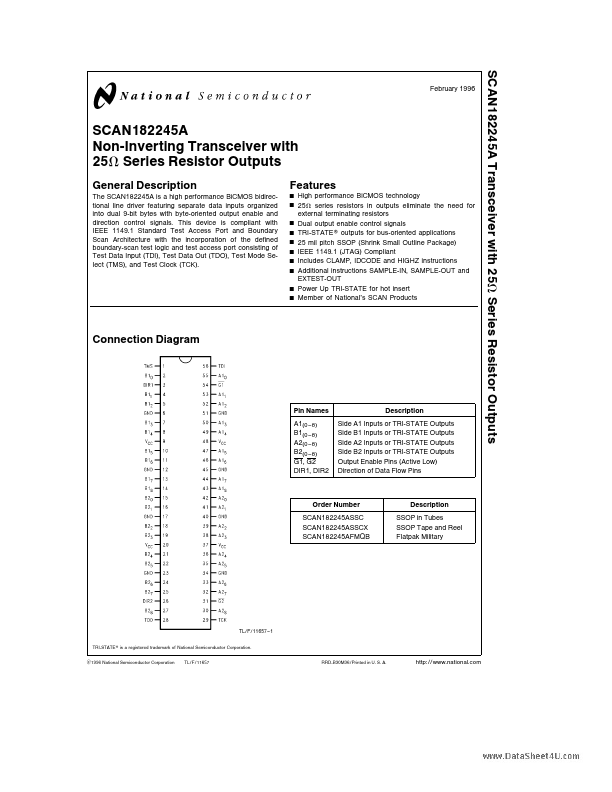

Connection Diagram

Pin Names A1(0- 8) B1(0- 8) A2(0- 8) B2(0- 8) G1 G2 DIR1 DIR2

Description

Side A1 Inputs or TRI-STATE Outputs Side B1 Inputs or TRI-STATE Outputs Side A2 Inputs or TRI-STATE Outputs Side B2 Inputs or TRI-STATE Outputs Output Enable Pins (Active Low) Direction of Data Flow Pins

Order Number SCAN182245ASSC SCAN182245ASSCX SCAN182245AFMQB

Description

SSOP in Tubes SSOP Tape and Reel Flatpak Military

TL F 11657

- 1

TRI-STATE is a registered trademark of National Semiconductor Corporation C1996 National Semiconductor Corporation TL F 11657 RRD-B30M36 Printed in U S A http

national

Truth Tables

Inputs G1 L L L L H DIR1 L L H H X H L H L Z A1(0

- 8) B1(0

- 8) H L H L Z

Functional Description

The SCAN182245A consists of two sets of nine non-inverting bidirectional buffers with TRI-STATE outputs and is intended for bus-oriented applications Direction pins (DIR1 and DIR2) LOW enables data from B ports to A ports when HIGH enables data from A ports to B ports The Output Enable pins (G1 and...