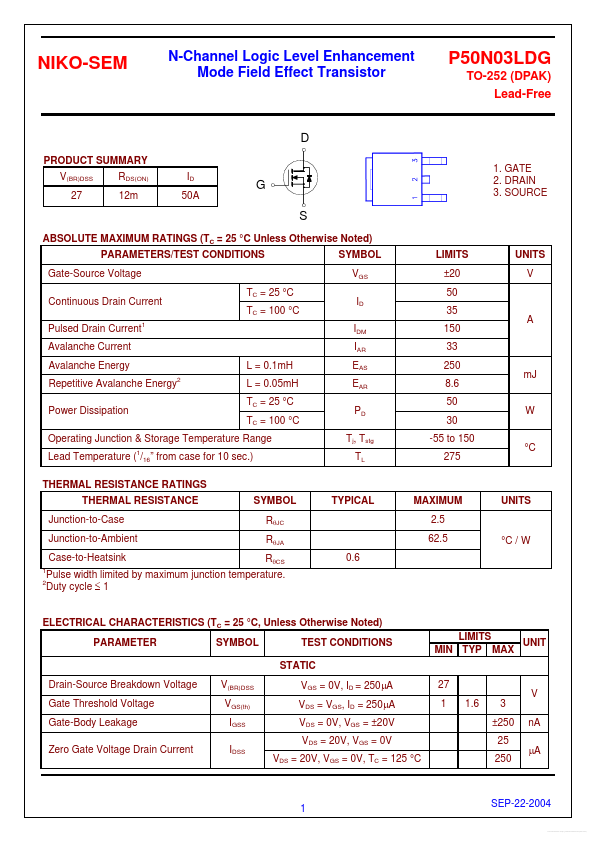

| Part | P50N03LDG |

|---|---|

| Description | N-Channel Logic Level Enhancement Mode Field Effect Transistor |

| Category | Transistor |

| Manufacturer | Niko-Sem |

| Size | 304.73 KB |

Pricing from 0.111 USD, available from UnikeyIC and Unikeyic (ICkey).

Price & Availability

| Seller | Inventory | Price Breaks | Buy |

|---|---|---|---|

| UnikeyIC | 12500 | 50+ : 0.111 USD 5000+ : 0.1091 USD 7500+ : 0.1064 USD |

View Offer |

| Unikeyic (ICkey) | 12500 | 50+ : 0.111 USD 5000+ : 0.1091 USD 7500+ : 0.1064 USD |

View Offer |

Similar Parts

| Part Number | Manufacturer | Description |

|---|---|---|

| P50N03LTG | UNIKC | N-Channel MOSFET |

| P50N06 | STMicroelectronics | STP50N06 |

| P50N05L | Fairchild Semiconductor | N-Channel Power MOSFETs |