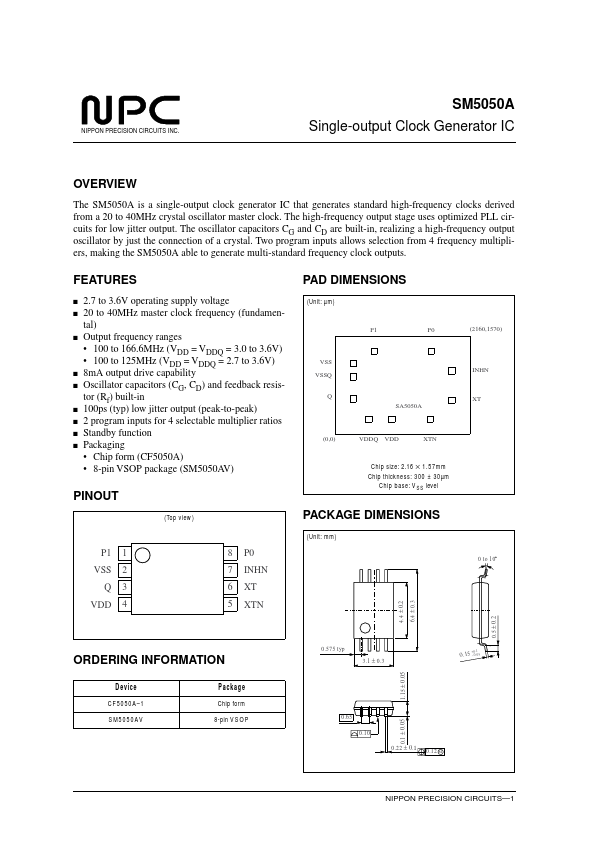

| Part | SM5050A |

|---|---|

| Description | Single-output Clock Generator |

| Manufacturer | Nippon Precision Circuits Inc |

| Size | 76.00 KB |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| SM5050-8 | RFM | 8-Terminal Ceramic |

| SM5059 | Semikron Danfoss | Surface mount diode |

| SM5059 | Diotec Semiconductor | Standard Recovery SMD Rectifier Diodes |