SM5852FS

SM5852FS is Digital Dynamic Bass Boost LSI manufactured by Nippon Precision Circuits Inc.

NIPPON PRECISION CIRCUITS INC.

Digital Dynamic Bass Boost LSI

OVERVIEW

The SM5852FS is a digital signal processor IC that performs DDBB (digital dynamic bass boost) processing for use in digital audio reproduction equipment. It is designed for use with a 44.1 kHz sampling frequency.

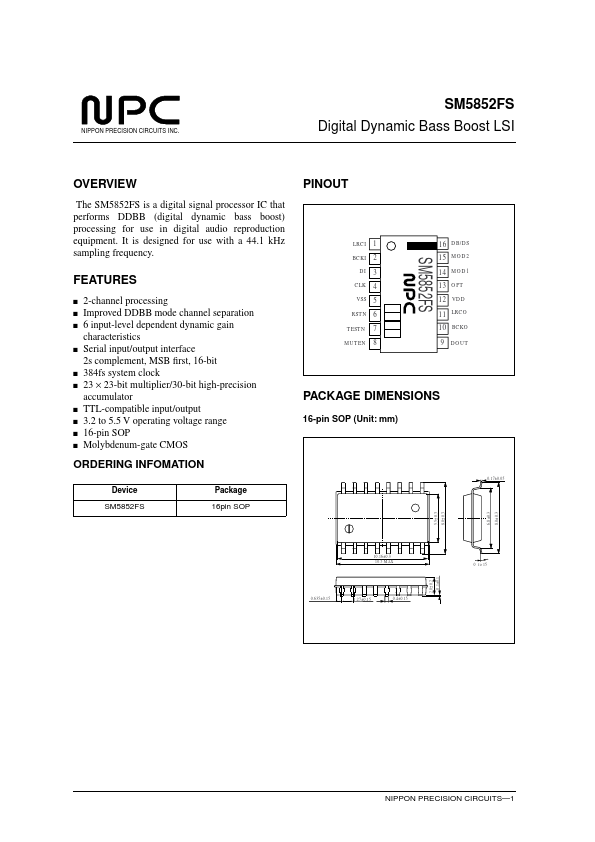

PINOUT

LRCI BCKI DI CLK VSS RSTN TESTN MUTEN

1 2 3 4 5 6 7 8

16 15 14 13 12 11 10 9

DB/DS MOD2 MOD1 OPT VDD LRCO BCKO DOUT

Features s s s s s s s s s s

2-channel processing Improved DDBB mode channel separation 6 input-level dependent dynamic gain characteristics Serial input/output interface 2s plement, MSB first, 16-bit 384fs system clock 23 × 23-bit multiplier/30-bit...