SM8703AV

SM8703AV is Clock Generator manufactured by Nippon Precision Circuits Inc.

OVERVIEW

The SM8703AV is a 27 MHz master clock, 5-system output clock generator for MPEG2 system. It has 2 builtin PLLs that, with the addition of a single crystal oscillator element, can generate 384fs, 512fs and 768fs clocks which are necessary for MPEG2 system, plus independent fixed-frequency 27 MHz and 33.8688 MHz output clocks. Each output can stop unused output by using disable function, therefore, unnecessary radiation can be suppressed. Also, visual and audio synchronous is not disrupted since each output frequency is kept in the normal ratio. Supported sampling frequencies (fs) include 44.1 or 48 k Hz.

FEATURES s

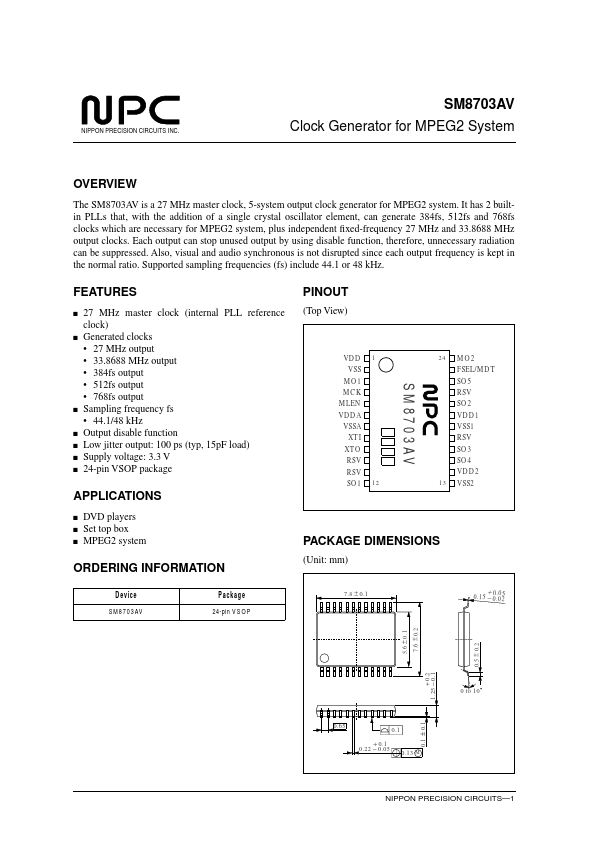

PINOUT

(Top View) s s s s s s

27 MHz master clock (internal PLL reference clock) Generated clocks

- 27 MHz output

- 33.8688 MHz output

- 384fs output

- 512fs output

- 768fs output Sampling frequency fs

- 44.1/48 k Hz Output disable function Low jitter output: 100 ps (typ, 15p F load) Supply voltage: 3.3 V 24-pin VSOP package

VDD VSS MO1 MCK MLEN VDDA VSSA XTI XTO RSV RSV SO1

MO2 FSEL/MDT SO5 RSV SO2 VDD1 VSS1 RSV SO3 SO4 VDD2 VSS2

APPLICATIONS s s s

DVD players Set top box MPEG2 system

PACKAGE DIMENSIONS

(Unit: mm)

7.8 ± 0.1

ORDERING INFORMATION

D e vice S M 8 7 0 3 AV P ackag e 24-pin V S O P

+ 0.05 0.15

- 0.02

5.6 ± 0.1

7.6 ± 0.2

+ 0.2 1.25

- 0.1

0 to 10

0.65 + 0.1 0.22

- 0.05

0.13 M

NIPPON PRECISION CIRCUITS- 1

0.1 ± 0.1

0.5 ± 0.2

BLOCK...