74ACT05

Features

- Outputs Source/Sink 24 m A

- ′ACT05 Has TTL patible Inputs

- These are Pb- Free Devices

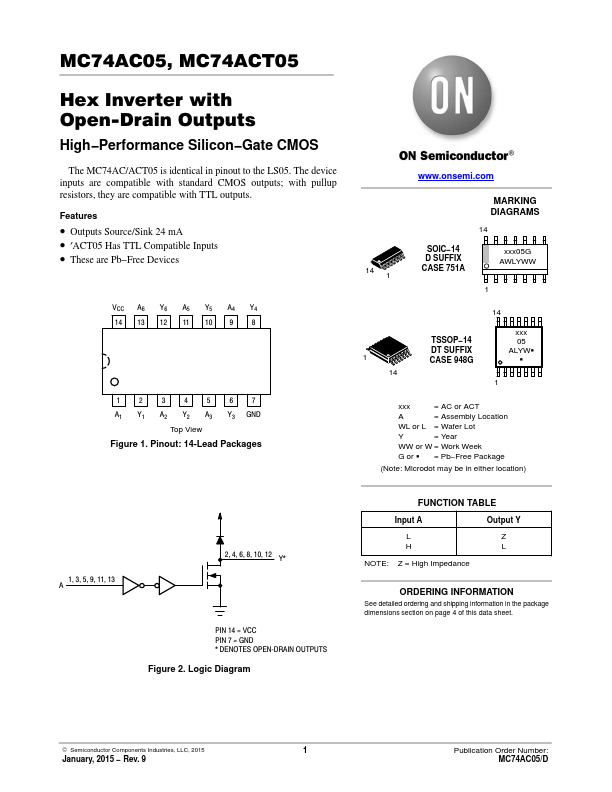

VCC A6 Y6 A5 Y5 A4 Y4 14 13 12 11 10 9 8

1234567 A1 Y1 A2 Y2 A3 Y3 GND

Top View Figure 1. Pinout: 14-Lead Packages

.onsemi.

14 1

MARKING DIAGRAMS

SOIC- 14 D SUFFIX CASE 751A xxx05G AWLYWW

1 14

TSSOP- 14 DT SUFFIX CASE 948G

14 xxx 05 ALYWG G

1 xxx = AC or ACT A = Assembly Location WL or L = Wafer Lot Y = Year WW or W = Work Week G or G = Pb- Free Package

(Note: Microdot may be in either location)

1, 3, 5, 9, 11, 13 A

2, 4, 6, 8, 10, 12 Y-

PIN 14 = VCC PIN 7 = GND

- DENOTES OPEN‐DRAIN OUTPUTS

Figure 2. Logic Diagram

FUNCTION TABLE

Input A

Output Y

LZ HL

NOTE: Z = High...