ASM162

ASM162 is uP Supervisory Circuit manufactured by onsemi.

- Part of the ASM161 comparator family.

- Part of the ASM161 comparator family.

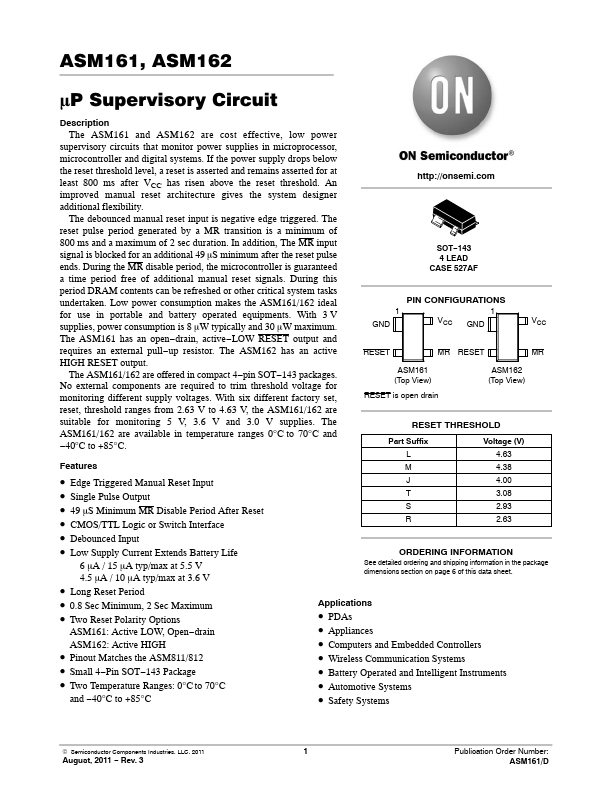

ASM161, ASM162 mP Supervisory Circuit

Description

The ASM161 and ASM162 are cost effective, low power supervisory circuits that monitor power supplies in microprocessor, microcontroller and digital systems. If the power supply drops below the reset threshold level, a reset is asserted and remains asserted for at least 800 ms after VCC has risen above the reset threshold. An improved manual reset architecture gives the system designer additional flexibility.

The debounced manual reset input is negative edge triggered. The reset pulse period generated by a MR transition is a minimum of 800 ms and a maximum of 2 sec duration. In addition, The MR input signal is blocked for an additional 49...