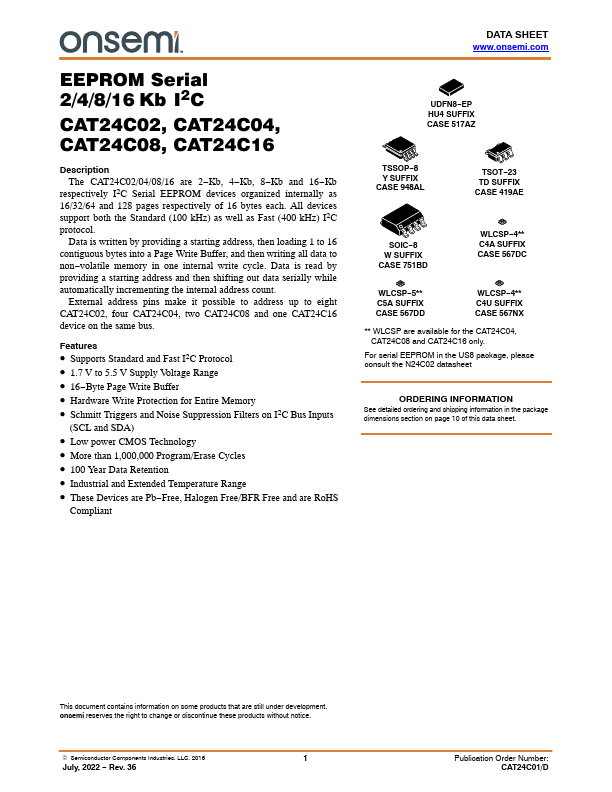

CAT24C04

Overview

- Supports Standard and Fast I2C Protocol

- 1.7 V to 5.5 V Supply Voltage Range

- 16-Byte Page Write Buffer

- Hardware Write Protection for Entire Memory

- Schmitt Triggers and Noise Suppression Filters on I2C Bus Inputs (SCL and SDA)

- Low power CMOS Technology

- More than 1,000,000 Program/Erase Cycles

- 100 Year Data Retention

- Industrial and Extended Temperature Range

- These Devices are Pb-Free, Halogen Free/BFR Free and are RoHS Compliant