CAV25512

CAV25512 is 512-Kb SPI Serial CMOS EEPROM manufactured by onsemi.

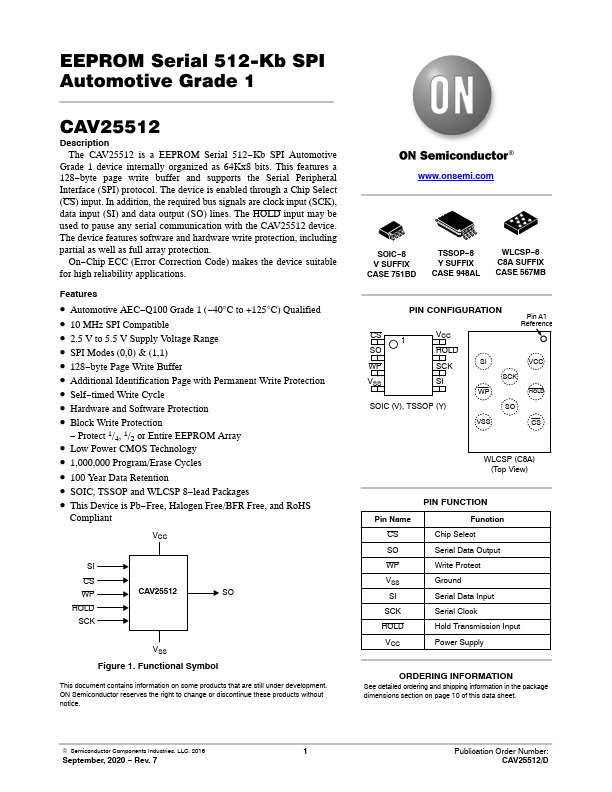

EEPROM Serial 512-Kb SPI Automotive Grade 1

Description The CAV25512 is a EEPROM Serial 512- Kb SPI Automotive

Grade 1 device internally organized as 64Kx8 bits. This Features a 128- byte page write buffer and supports the Serial Peripheral Interface (SPI) protocol. The device is enabled through a Chip Select (CS) input. In addition, the required bus signals are clock input (SCK), data input (SI) and data output (SO) lines. The HOLD input may be used to pause any serial munication with the CAV25512 device. The device Features software and hardware write protection, including partial as well as full array protection.

On- Chip ECC (Error Correction Code) makes the device suitable...