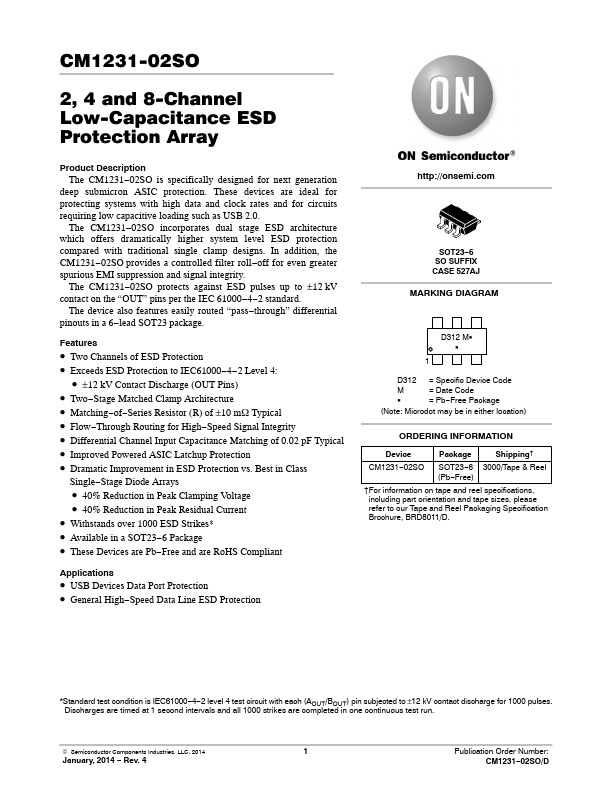

CM1231-02SO

Description

The CM1231- 02SO is specifically designed for next generation deep submicron ASIC protection. These devices are ideal for protecting systems with high data and clock rates and for circuits requiring low capacitive loading such as USB 2.0.

The CM1231- 02SO incorporates dual stage ESD architecture which offers dramatically higher system level ESD protection pared with traditional single clamp designs. In addition, the CM1231- 02SO provides a controlled filter roll- off for even greater spurious EMI suppression and signal integrity.

The CM1231- 02SO protects against ESD pulses up to ±12 k V contact on the “OUT” pins per the IEC 61000- 4- 2 standard.

The device also features easily routed “pass- through” differential pinouts in a 6- lead SOT23 package.

Features

- Two Channels of ESD Protection

- Exceeds ESD Protection to IEC61000- 4- 2 Level 4:

- ±12 k V Contact Discharge (OUT Pins)

- Two- Stage Matched Clamp Architecture

- Matching- of- Series Resistor (R) of ±10 m W Typical

- Flow- Through...