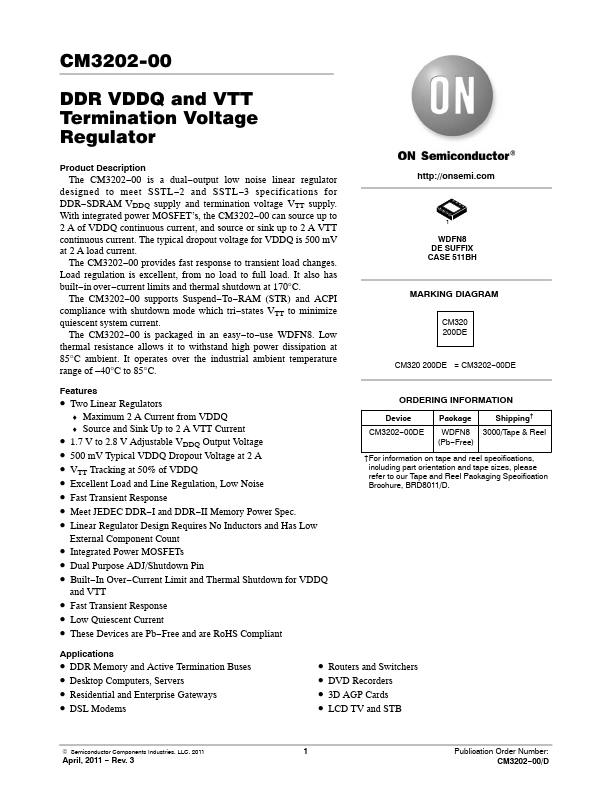

CM3202-00 Overview

Key Features

- Two Linear Regulators

- Maximum 2 A Current from VDDQ

- Source and Sink Up to 2 A VTT Current

- 1.7 V to 2.8 V Adjustable VDDQ Output Voltage

- 500 mV Typical VDDQ Dropout Voltage at 2 A

- VTT Tracking at 50% of VDDQ

- Excellent Load and Line Regulation, Low Noise

- Fast Transient Response

- Meet JEDEC DDR-I and DDR-II Memory Power Spec

- Linear Regulator Design Requires No Inductors and Has Low External Component Count