HC125AG

Features

- Output Drive Capability: 15 LSTTL Loads

- Outputs Directly Interface to CMOS, NMOS, and TTL

- Operating Voltage Range: 2.0 to 6.0 V

- Low Input Current: 1.0 m A

- High Noise Immunity Characteristic of CMOS Devices

- In pliance with the JEDEC Standard No. 7 A Requirements

- Chip plexity: 72 FETs or 18 Equivalent Gates

- NLV Prefix for Automotive and Other Applications Requiring

Unique Site and Control Change Requirements; AEC- Q100 Qualified and PPAP Capable

- These Devices are Pb- Free, Halogen Free/BFR Free and are Ro HS pliant

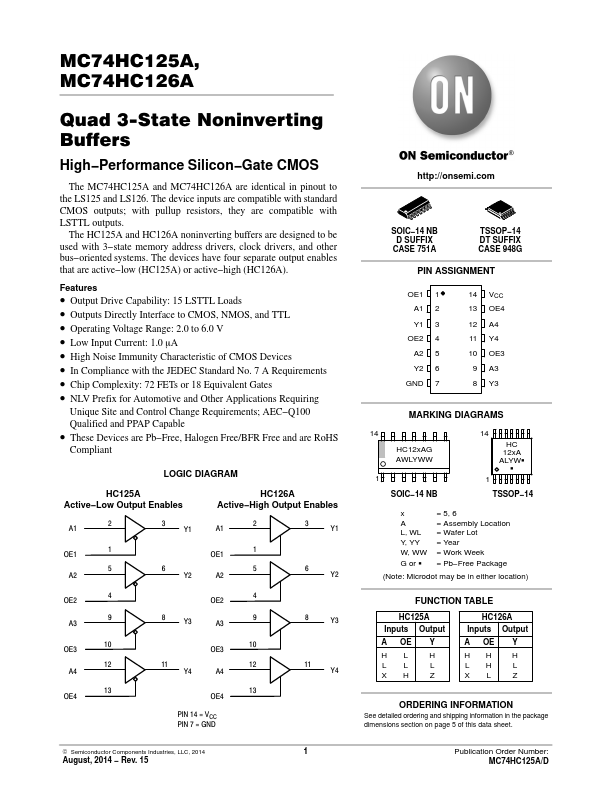

LOGIC DIAGRAM

HC125A Active- Low Output Enables

HC126A Active- High Output Enables

A1

3 Y1

A1

Y1

OE1

5 A2

OE1

Y2

A2

6 Y2

OE2

9 A3

OE2

8...