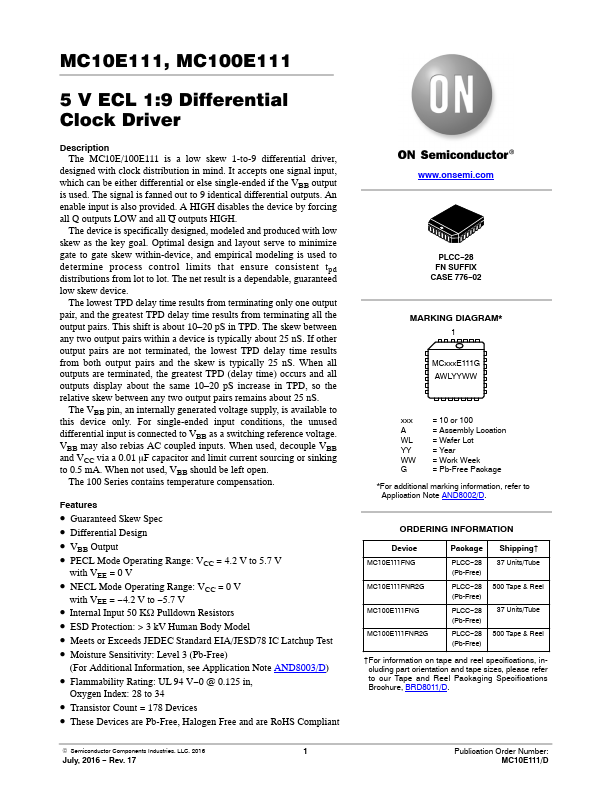

| Part | MC100E111 |

|---|---|

| Description | 1:9 DIFFERENTIAL CLOCK DRIVER |

| Manufacturer | onsemi |

| Size | 155.24 KB |

Related Datasheets

| Part Number | Manufacturer | Description |

|---|---|---|

| MC100E111 | Motorola Semiconductor | 1:9 DIFFERENTIAL CLOCK DRIVER |

| MC100E112 | Motorola Semiconductor | QUAD DRIVER |

| MC100E116 | Motorola Semiconductor | QUINT DIFFERENTIAL LINE RECEIVER |