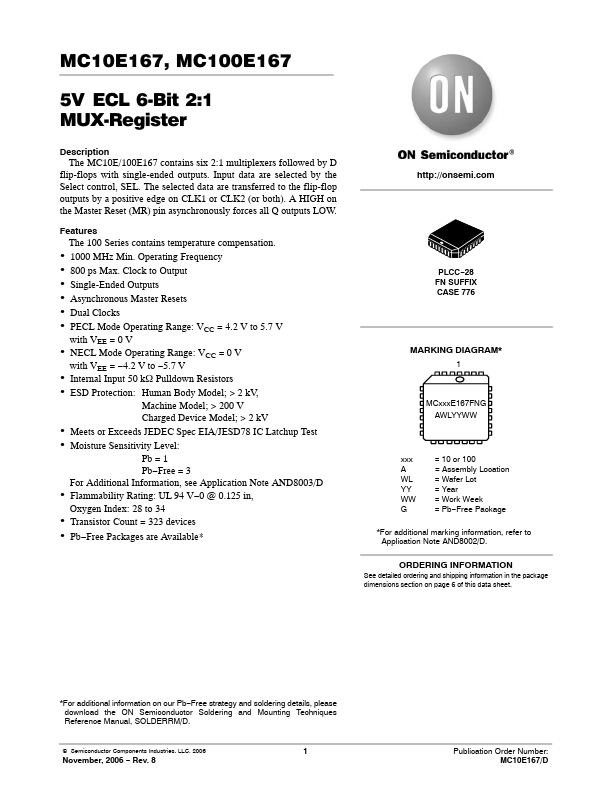

MC100E167

Description

The MC10E/100E167 contains six 2:1 multiplexers followed by D flip-flops with single-ended outputs. Input data are selected by the Select control, SEL. The selected data are transferred to the flip-flop outputs by a positive edge on CLK1 or CLK2 (or both). A HIGH on the Master Reset (MR) pin asynchronously forces all Q outputs LOW.

Features http://onsemi.

- -

- -

- -

- -

- -

- -

- -

The 100 Series contains temperature pensation. 1000 MHz Min. Operating Frequency 800 ps Max. Clock to Output Single-Ended Outputs Asynchronous Master Resets Dual Clocks PECL Mode Operating Range: VCC = 4.2 V to 5.7 V with VEE = 0 V NECL Mode Operating Range: VCC = 0 V with VEE =

- 4.2 V to

- 5.7 V Internal Input 50 k W Pulldown Resistors ESD Protection: Human Body Model; > 2 k V, Machine Model; > 200 V Charged Device Model; > 2 k V Meets or Exceeds JEDEC Spec EIA/JESD78 IC Latchup Test Moisture Sensitivity Level: Pb = 1 Pb- Free = 3 For Additional Information, see Application Note AND8003/D...