MC100E310

Description

The MC100E310 is a low voltage, low skew 2:8 differential ECL fanout buffer designed with clock distribution in mind.

Key Features

- Dual Differential Fanout Buffers

- 200 ps Part-to-Part Skew

- 50 ps Output-to-Output Skew

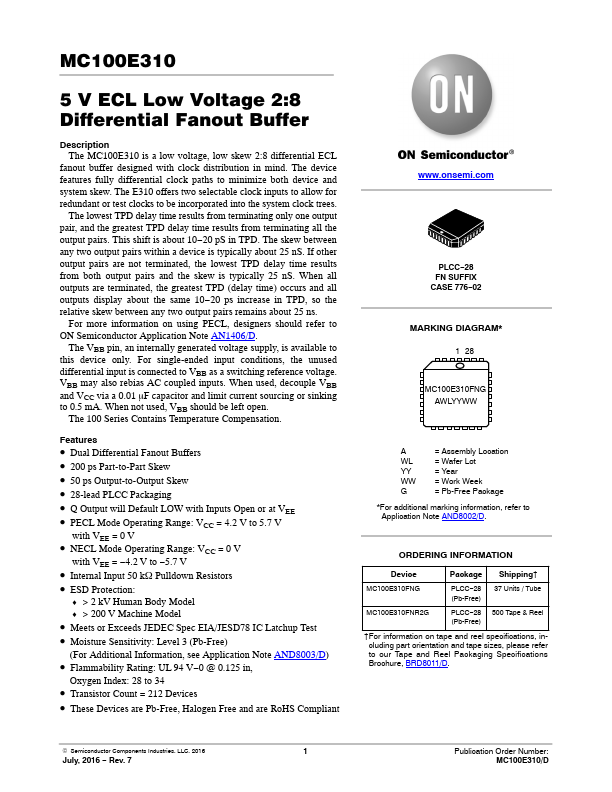

- 28-lead PLCC Packaging

- Q Output will Default LOW with Inputs Open or at VEE

- PECL Mode Operating Range: VCC = 4.2 V to 5.7 V with VEE = 0 V

- NECL Mode Operating Range: VCC = 0 V with VEE = -4.2 V to -5.7 V

- Internal Input 50 kW Pulldown Resistors

- ESD Protection

- > 2 kV Human Body Model