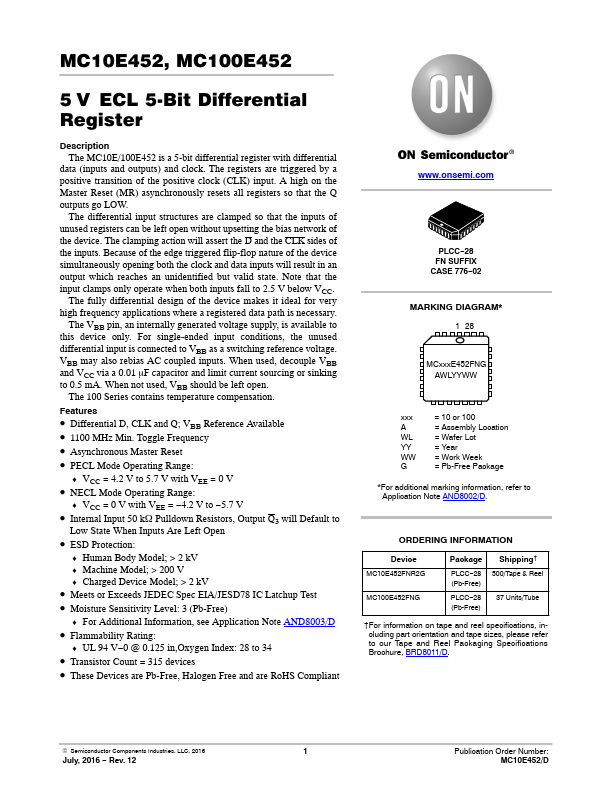

MC100E452

Description

The MC10E/100E452 is a 5-bit differential register with differential data (inputs and outputs) and clock.

Key Features

- Differential D, CLK and Q; VBB Reference Available

- 1100 MHz Min. Toggle Frequency

- Asynchronous Master Reset

- PECL Mode Operating Range

- VCC = 4.2 V to 5.7 V with VEE = 0 V

- NECL Mode Operating Range

- VCC = 0 V with VEE = -4.2 V to -5.7 V

- Internal Input 50 kW Pulldown Resistors, Output Q3 will Default to Low State When Inputs Are Left Open

- ESD Protection

- Human Body Model; > 2 kV