MC100EP016A

MC100EP016A is 3.3V ECL 8-Bit Synchronous Binary Up Counter manufactured by onsemi.

Description

The MC100EP016A is a high- speed synchronous, presettable, cascadeable 8- bit binary counter. Architecture and operation are the same as the ECLin PS™ family MC100E016 with higher operating speed.

The counter features internal feedback to TC gated by the TCLD (Terminal Count Load) pin. When TCLD is LOW (or left open, in which case it is pulled LOW by the internal pulldowns), the TC feedback is disabled, and counting proceeds continuously, with TC going LOW to indicate an all- one state. When TCLD is HIGH, the TC feedback causes the counter to automatically reload upon TC = LOW, thus functioning as a programmable counter. The Qn outputs do not need to be terminated for the count function to operate properly. To minimize noise and power, unused Q outputs should be left unterminated.

COUT and COUT provide differential outputs from a single, non- cascaded counter or divider application. COUT and COUT should not be used in cascade configuration. Only TC should be used for a counter or divider cascade chain output.

A differential clock input has also been added to improve performance.

The 100 Series contains temperature pensation.

Features

- 550 ps Typical Propagation Delay

- Operation Frequency > 1.3 GHz is 30% Faster than MC100EP016

- PECL Mode Operating Range: VCC = 3.0 V to 3.6 V with VEE = 0 V

- NECL Mode Operating Range: VCC = 0 V with VEE =

- 3.0 V to

- 3.6 V

- Open Input Default State

- Safety Clamp on Clock Inputs

- Internal TC Feedback (Gated)

- Addition of COUT and COUT

- 8- Bit

- Differential Clock Input

- VBB Output

- Fully Synchronous Counting and TC Generation

- Asynchronous Master Reset

- Pb- Free Packages are Available

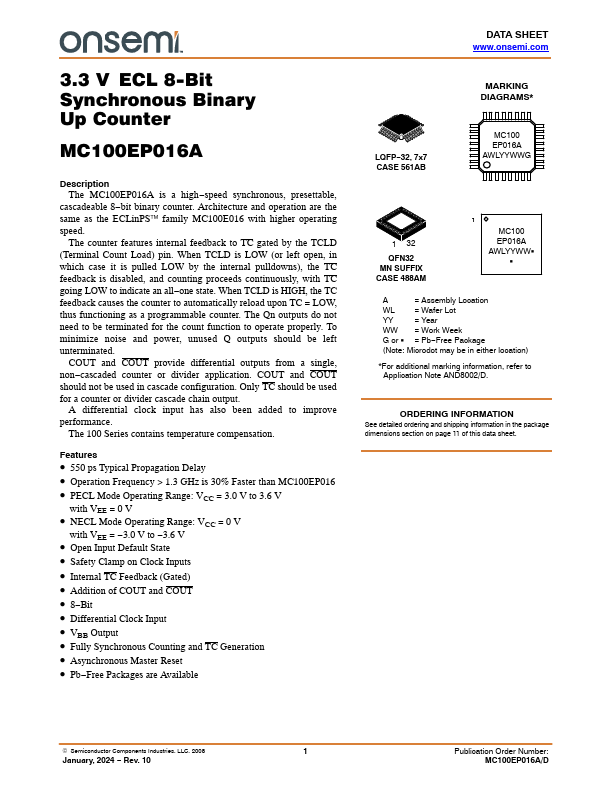

LQFP- 32, 7x7 CASE 561AB

DATA SHEET .onsemi.

MARKING DIAGRAMS-

MC100 EP016A AWLYYWWG

1 32

QFN32 MN SUFFIX CASE 488AM

MC100 EP016A AWLYYWWG

= Assembly Location

WL = Wafer Lot

= Year

WW = Work Week

G or G = Pb- Free Package

(Note: Microdot may be in either...