MC100LVEL51 Overview

Key Specifications

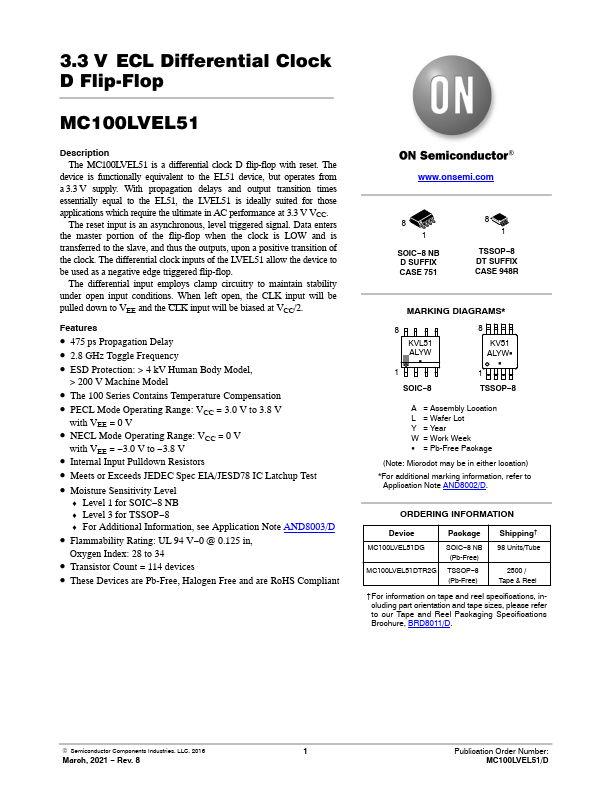

Package: SOP

Mount Type: Surface Mount

Pins: 8

Operating Voltage: 3.3 V

Description

The MC100LVEL51 is a differential clock D flip-flop with reset. The device is functionally equivalent to the EL51 device, but operates from a 3.3 V supply.

Key Features

- 475 ps Propagation Delay

- 2.8 GHz Toggle Frequency

- ESD Protection: > 4 kV Human Body Model, > 200 V Machine Model

- The 100 Series Contains Temperature Compensation

- PECL Mode Operating Range: VCC = 3.0 V to 3.8 V with VEE = 0 V

- NECL Mode Operating Range: VCC = 0 V with VEE = -3.0 V to -3.8 V

- Internal Input Pulldown Resistors

- Meets or Exceeds JEDEC Spec EIA/JESD78 IC Latchup Test

- Moisture Sensitivity Level

- Level 1 for SOIC-8 NB