MC100LVEP111 Overview

Key Specifications

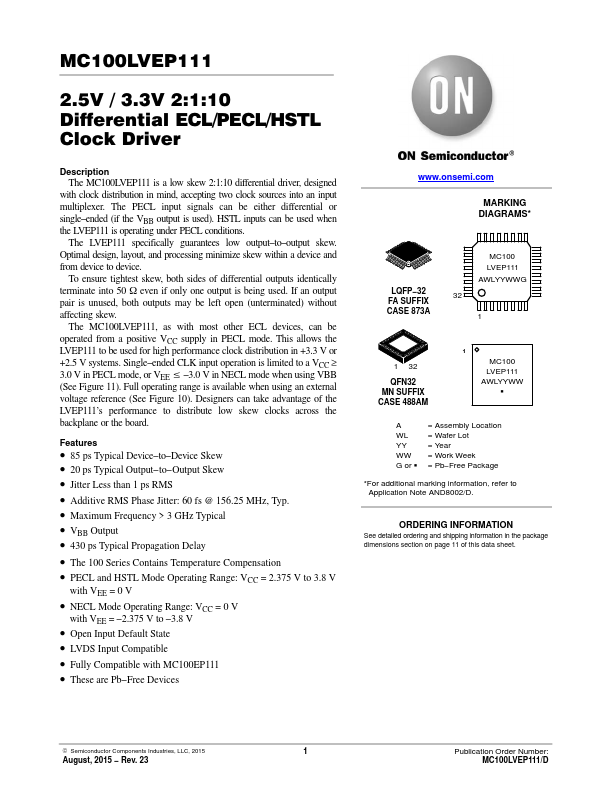

Package: QFN

Mount Type: Surface Mount

Pins: 32

Operating Voltage: 2.5 V

Description

The MC100LVEP111 is a low skew 2:1:10 differential driver, designed with clock distribution in mind, accepting two clock sources into an input multiplexer. The PECL input signals can be either differential or single-ended (if the VBB output is used).