MC10H113

MC10H113 is Quad Exclusive OR Gate manufactured by onsemi.

Description

The MC10H113 is a Quad Exclusive OR Gate with an enable mon to all four gates. The outputs may be wire- ORed together to perform a 4- bit parison function (A = B). The enable is active LOW.

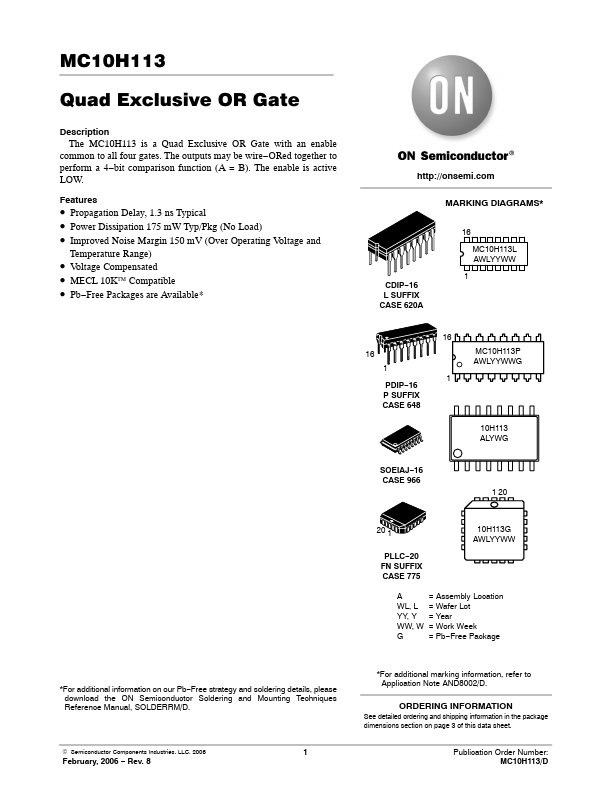

Features http://onsemi. MARKING DIAGRAMS-

16 MC10H113L AWLYYWW CDIP- 16 L SUFFIX CASE 620A 1

- Propagation Delay, 1.3 ns Typical

- Power Dissipation 175 m W Typ/Pkg (No Load)

- Improved Noise Margin 150 m V (Over Operating Voltage and

- -

- Temperature Range) Voltage pensated MECL 10K™ patible Pb- Free Packages are Available-

16 16 1 PDIP- 16 P SUFFIX CASE 648 1 MC10H113P AWLYYWWG

10H113 ALYWG

SOEIAJ- 16 CASE 966 1 20

20 1 PLLC- 20 FN SUFFIX CASE 775 A WL, L YY, Y WW, W G

10H113G AWLYYWW

= Assembly Location = Wafer Lot = Year = Work Week = Pb- Free Package

- For additional information on our Pb- Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

- For additional marking information, refer to Application Note AND8002/D.

ORDERING INFORMATION

See detailed ordering and shipping information in the package dimensions section on page 3 of this data sheet.

© Semiconductor ponents Industries, LLC, 2006

February, 2006

- Rev. 8

Publication Order Number: MC10H113/D

E 4 5 9 2

TRUTH TABLE IN L H L H X E OUTPUT L L L L L H H H L L

6 7

VCC1 Aout Bout Ain Ain Bin Bin

1 2 3 4 5 6 7 8

16 15 14 13 12 11 10 9

VCC2 Dout Cout Din Din Cin Cin Enable

10 11

VCC1 = Pin 1 VCC2 = Pin 16 14 VEE = Pin 8

12 13

Pin assignment is for Dual- in- Line Package.

Figure 1. Logic Diagram

Figure 2. Pin...