MC74VHCT573A Description

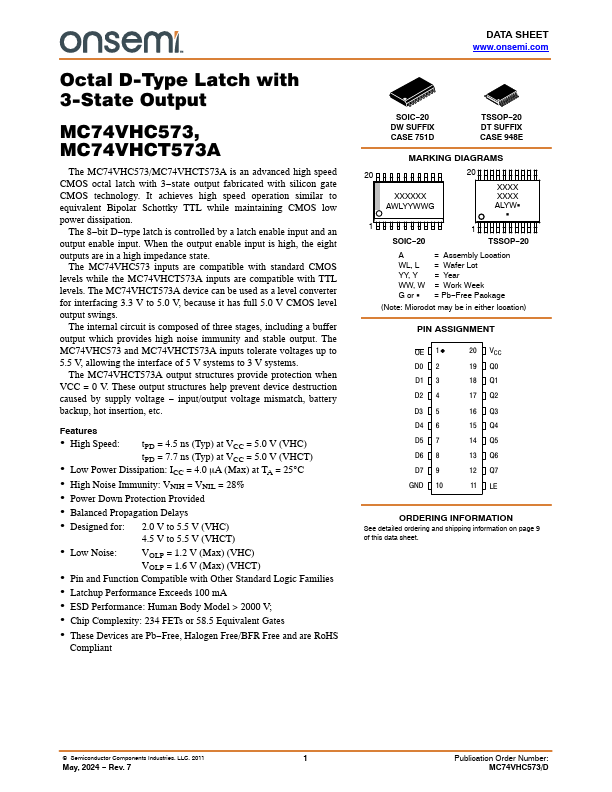

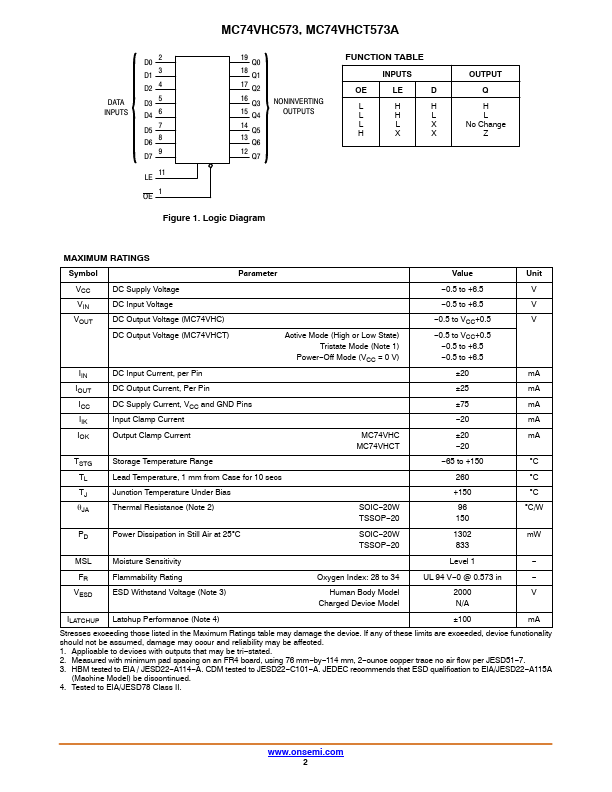

Octal D-Type Latch with 3-State Output MC74VHC573, MC74VHCT573A The MC74VHC573/MC74VHCT573A is an advanced high speed CMOS octal latch with 3−state output fabricated with silicon gate CMOS technology. It achieves high speed operation similar to equivalent Bipolar Schottky TTL while maintaining CMOS low power dissipation. The 8−bit D−type latch is controlled by a latch enable input and an output enable input.

MC74VHCT573A Key Features

- High Speed: tPD = 4.5 ns (Typ) at VCC = 5.0 V (VHC)

- Low Power Dissipation: ICC = 4.0 mA (Max) at TA = 25C

- High Noise Immunity: VNIH = VNIL = 28%

- Power Down Protection Provided

- Balanced Propagation Delays

- Designed for: 2.0 V to 5.5 V (VHC)

- Low Noise

- Pin and Function patible with Other Standard Logic Families

- Latchup Performance Exceeds 100 mA

- ESD Performance: Human Body Model > 2000 V