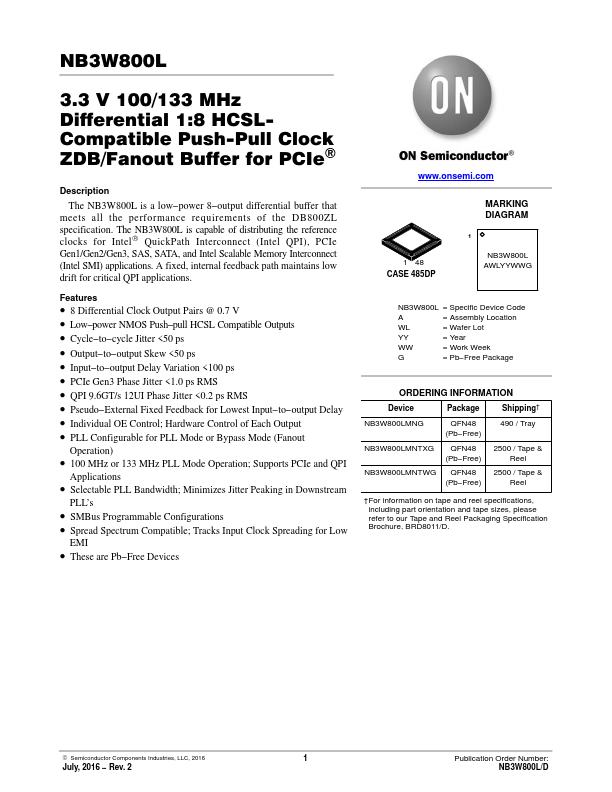

NB3W800L

Description

The NB3W800L is a low-power 8-output differential buffer that meets all the performance requirements of the DB800ZL specification. The NB3W800L is capable of distributing the reference clocks for Intel® QuickPath Interconnect (Intel QPI), PCIe Gen1/Gen2/Gen3, SAS, SATA, and Intel Scalable Memory Interconnect (Intel SMI) applications.

Key Features

- 8 Differential Clock Output Pairs @ 0.7 V

- Low-power NMOS Push-pull HCSL Compatible Outputs

- Cycle-to-cycle Jitter <50 ps

- Output-to-output Skew <50 ps

- Input-to-output Delay Variation <100 ps

- PCIe Gen3 Phase Jitter <1.0 ps RMS

- QPI 9.6GT/s 12UI Phase Jitter <0.2 ps RMS

- Pseudo-External Fixed Feedback for Lowest Input-to-output Delay

- Individual OE Control; Hardware Control of Each Output